# Passively Probing an InfiniBand System with an Agilent 16700 Series Logic Analysis System

**Product Note**

## **Table of Contents**

| InfiniBand Logic Analysis Support1                                 |

|--------------------------------------------------------------------|

| Description                                                        |

| Generic Block Diagram                                              |

| Agilent Technologies HDMP-2634 SerDes ASIC's2                      |

| Logic Analysis Features                                            |

| Termination Networks                                               |

| Built-in Termination Networks                                      |

| Discrete Termination Networks                                      |

| • Routing Techniques5                                              |

| Logic Analyzer Connectors7                                         |

| Mictor Connectors7                                                 |

| Connector Placement Techniques7                                    |

| Mictor Connector Pinout7                                           |

| Appendix                                                           |

| Supported Logic Analyzer Modules for InfiniBand8                   |

| <ul> <li>Probing Part Numbers and Ordering Information8</li> </ul> |

| Related Literature8                                                |

| • Technical Support8                                               |

## InfiniBand Logic Analysis Support

## Description

This product note describes the techniques required for passively probing a parallel InfiniBand channel with an Agilent 16700 Series logic analysis system.

## **Glossary of Terms**

| Terminology | Description                             |

|-------------|-----------------------------------------|

| SerDes      | Serializer / De-serializer ASIC         |

|             | (Typically pronounced "Sir-Deez")       |

| IBA         | InfiniBand Architecture                 |

| SUT         | Signal Under Test                       |

| SMT         | Surface Mount                           |

| PCB         | Printed Circuit Board                   |

| LVTTL       | Low Voltage TTL Logic                   |

| SSTL-2      | Stub Series Terminated Logic (2.5 Volt) |

| Mictor      | Amp Matched Impedance Connector         |

|             | (Used with high-density logic analyzer  |

|             | cables)                                 |

| 10b/8b      | InfiniBand data coding scheme           |

## **Generic Block Diagram**

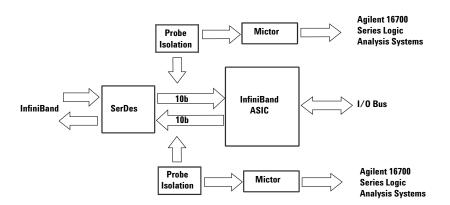

Due to loading restrictions and logic analyzer performance, probing raw differential InfiniBand data with a logic analyzer is nearly impossible. The logic analyzer must probe the de-serialized data to passively measure traffic on InfiniBand channels. For systems utilizing discrete SerDes chips, the parallel data is available to route to logic analyzer connectors. Mictor connectors, along with optional isolation circuitry to minimize logic analyzer loading on the parallel data, are connected to the 10b bus running between the SerDes and the InfiniBand controller ASIC. A simplified block diagram of this connection scheme is shown in Figure 1.

Systems that contain the SerDes built into a custom ASIC will require an auxiliary bus to output the parallel data to the ASIC pins to be compatible with a logic analyzer. Without an external SerDes or auxiliary bus the 10b traffic is not observable and cannot be probed by the logic analyzer.

## Agilent HDMP-2634 SerDes ASIC's

This product note supports probing and analysis of the Agilent HDMP-2634 SerDes. The Agilent SerDes drives 10b encoded data at 10 bits x 125 MHz (DDR) at an SSTL-2 logic level. The data is sampled by the logic analyzer on both the rising and falling edge of the clock for an effective data rate of 250 MHz. Data is displayed on the logic analyzer in raw 10b encoded format, unless a postprocessing tool is used to convert and decode the data.

## **Logic Analysis Features**

## Triggering

The Agilent 16700 Series logic analysis systems typically contain 4 sequence levels for triggering on data streams. Since the data is effectively double data rate, the 16700 Series system must run in "Turbo" mode, which reduces the number of available sequence levels to six.

Figure 1. Block diagram of Mictor connectors connected to the 10b bus running between the SerDes and the InfiniBand controller ASIC

### **Generic Data Display**

The 16700 Series system contains a waveform viewer and linear listing window to view sampled data. Both of these tools display the data in the raw format that is sampled by the logic analyzer.

**Post Processing and Custom Displays**

A tool development kit for the 16700 Series system can be used to create powerful post-processing tools that perform 8b data and packet decoding. This capability is currently available to InfiniBand developers who design Mictor connectors into their InfiniBand host channel adapter (HCA) and target channel adapter (TCA) systems. Figure 2 shows an example of the kind of packet decoding that can be performed. Full realtime acquisition of InfiniBand traffic along with concurrent transactions on other system buses such as PCI-X, CPU buses, PC266 DDR and Rambus<sup>®</sup> are supported. Events on one bus can trigger measurements on all buses with time-correlated views of all bus events.

| PA-In Decode     File Window Edit Options Invasm Source     Help |                |             |                 |             |                                  |

|------------------------------------------------------------------|----------------|-------------|-----------------|-------------|----------------------------------|

|                                                                  |                |             |                 |             |                                  |

| State                                                            | Number PA_DATA | _IN 8-bit E | ata BadDisparit | y Disparity | Packet Decode                    |

| Decima                                                           | 1 Hex          | Hex         | Binary          | Twos        | Text                             |

|                                                                  |                |             |                 |             |                                  |

| -8246                                                            | 17C            | 00          | 0               | +001        | Comma (K28.5) - Skip Ordered Set |

| -8245                                                            | 343            | 00          | ŏ               | +001        | Skip Ordered Set                 |

| -8245                                                            | 343<br>343     | FF          | 0               | +001        | Skip Ordered Set                 |

| -8243                                                            | 343            | FF          | ŏ               | +001        | Skip Ordered Set                 |

| -3884                                                            | 17C            | 00          | ŏ               | +001        | Comma (K28.5) - Skip Ordered Set |

| -3883                                                            | 343            | ŏŏ          | ŏ               | +001        | Skip Ordered Set                 |

| -3882                                                            | 343            | FF          | ŏ               | +001        | Skip Ordered Set                 |

| -3881                                                            | 343            | FF          | ů<br>0          | +001        | Skip Ordered Set                 |

| -2100                                                            | 0.0<br>05B     | 00          | ů<br>0          | -001        | Start of Data Packet (K27.7)     |

| -2099                                                            | 236            | FO          | ů<br>0          | -001        | Infiniband Data Packet           |

| 2000                                                             | 200            |             |                 | 002         | Virtual Lane = 15 Decimal        |

|                                                                  |                |             |                 |             | Link Version = 0 Decimal         |

| -2098                                                            | OAD            | 02          | 0               | -001        | Service Level = 0 Decimal        |

|                                                                  |                |             |                 |             | Reserved = 0 Decimal             |

|                                                                  |                |             |                 |             | Link Next Header = 2 Hex         |

| -2097                                                            | 235            | FF          | 0               | -001        | Destination Local ID = ffff Hex  |

| -2096                                                            | 235            | FF          |                 | -001        |                                  |

| -2095                                                            | 0B9            | 00          |                 | -001        | Reserved = 00 Hex                |

|                                                                  |                |             |                 |             | Packet Length = 72 Decimal       |

| -2094                                                            | 2A7            | 48          |                 | +001        |                                  |

| -2093                                                            | 346            | 00          |                 | +001        | Source Local ID = 0007 Hex       |

| -2092                                                            | 0B8            | 07          |                 | -001        |                                  |

| -2091                                                            | 32B            | 64          |                 | +001        | Payload (Infiniband Data Packet) |

| -2090                                                            | 346            | 00          |                 | +001        | Payload (Infiniband Data Packet) |

| -2089                                                            | 1CA            | FF          |                 | +001        | Payload (Infiniband Data Packet) |

| -2088                                                            | 1CA            | FF          |                 | +001        | Payload (Infiniband Data Packet) |

| -2087                                                            | 346            | 00          | 0               | +001        | Payload (Infiniband Data Packet) |

Figure 2. Example of  $10b \ge 8b$  and InfiniBand protocol decode

## **Termination Networks**

Termination networks are required for probing a digital signal. The termination network isolates the logic analyzer cabling and sensing circuitry from the signal under test and provides a high impedance, low capacitance load at the probe point.

## **Built-in Termination Networks**

The first and simplest technique for probing the output of the SerDes ASIC is to use cabling from Agilent with the termination networks built into the cable tip (Agilent E5346A high-density cable).

Signals are simply routed on the printed circuit board (PCB) to Mictor connectors and terminated internally on the connection cable. Connector placement is critical to minimize the stub length and reflections on signals with fast rise times. However, even the best routing cannot eliminate the stubs completely since the path to the connector and the cable tip is a stub.

The general rule of thumb is to keep the stub length less than 1/5 the rise time of the signal under test (SUT). Whenever it is possible to route the signals within the previous constraints, use the built-in termination networks. They are designed for the Agilent logic analysis systems and are compensated to provide flat frequency response between the signal under test and the logic analyzer input comparators.Refer to the following equations for deciding whether to use built-in termination networks.

$$\begin{split} &l_{\rm stub} \leq 1/5 \ {\rm x} \ {\rm t}_{\rm rise \ time} \ / \ V_{\rm prop \ speed} \\ &l_{\rm stub} \leq 1/5 \ {\rm x} \ {\rm t}_{\rm rise \ time} \ / \ V_{\rm prop \ speed} \leq 1/5 \ {\rm x} \ 1000 \ {\rm ps} \ / \ (150 \ {\rm ps} \ / \ {\rm in}) \leq 1.3 \ '' \\ & (1 {\rm ns} \ {\rm rise \ time}) \\ &l_{\rm stub} \leq 1/5 \ {\rm x} \ {\rm t}_{\rm rise \ time} \ / \ V_{\rm prop \ speed} \leq 1/5 \ {\rm x} \ 500 \ {\rm ps} \ / \ (150 \ {\rm ps} \ / \ {\rm in}) \leq 0.65 \ '' \\ & (500 \ {\rm ps} \ {\rm rise \ time}) \end{split}$$

The Agilent SerDes has a 1-1.5 ns rise time, which requires traces to be kept between 1.3 - 2 inches in length.

## **Discrete Termination Networks**

When routing constraints prohibit using the built-in termination networks, external components can be designed into the circuit to increase the length between the logic analyzer connector and the signal under test. However, this is only recommended under rare cases when routing issues prohibit the use of standard cabling. Discrete termination networks are complex to design and beyond the scope of this document. Two solutions are provided for signals with 500 ps and 1 ns rise times.

The following sections describe the recommended termination network and how to select components for a target system.

#### **Designing a Discrete RCR Termination Network**

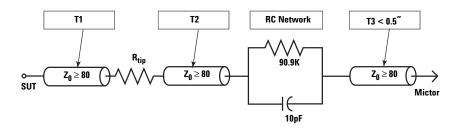

Figure 3. Schematic diagram for designing a discrete termination network

| SUT Rise<br>Time | T1 Length | T2 Length | T3 Length | T1/T2/T3<br>Impedance | R <sub>tip</sub> |

|------------------|-----------|-----------|-----------|-----------------------|------------------|

| ≥ 1ns            | ≤ 1.4″    | ≤ 1.4″    | ≤ 0.5″    | Z <sub>0</sub> ≥ 80 Ω | 196 Ω            |

| ≥ 500ps          | ≤ 0.7″    | ≤ 0.7″    | ≤ 0.5″    | $Z_0 \ge 80 \ \Omega$ | 215 Ω            |

Table 1. Key parameters for designing a discrete probing network

The key parameter to consider when designing a discrete probing network is the rise time of the signal under test. Maximum trace lengths and tip resistor values are dependent upon the rise time.

#### Note:

The Table 1 values are derived from complex equations that are a function of the logic analyzer connector and cabling electrical characteristics, input network, standard component values, trace impedance and length, and parasitic capacitance and inductance. It is beyond the scope of this document to provide these equations for general discussion. If the maximum trace lengths specified here are not sufficient to probe the signal under test, please consult an Agilent technical specialist.

T1, T2, and T3 are all 80W or higher PCB traces on the target system that connect the various components in the probing network. It is important to keep the trace impedance as high as possible. It is recommended that outer layers be used, which minimize the capacitance and maximize the impedance and propagation speeds. In general, design the trace on an outer layer with as high impedance as possible without implementing outof-the-ordinary design techniques such as ground plane cutouts. Keep the trace lengths within the tolerances specified in the table.

The tip resistor  $R_{tip}$  must be placed within the T1 length of the SUT. The trace length and tip resistor have been selected to provide maximum frequency response into the logic analyzer input network.

The RC network is connected to Rtip via a PCB trace T2, which should not exceed the T2 length. Use precision 0402 or 0603 SMT components for this network (1% R, 5% C).

The Mictor connector should be placed as close to the RC network as possible, not to exceed T3 length = 0.5 inches PCB trace length. The input impedance of the connector and logic analyzer cable is 120W. In practice it is very difficult to achieve a matched impedance PCB trace, resulting in an inevitable mismatch. To keep the reflections from degrading the setup and hold margins, the maximum length of T3 has been specified in Table 1.

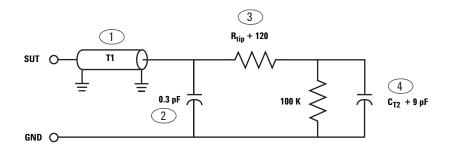

#### Figure 4. Equivalent load

The discrete probing network and the logic analyzer input can be modeled as shown in Figure 4.

- 1. T1 is a PCB trace transmission line specified in Table 1.  $R_{tip}$  is the sum of the tip resistor and the logic analyzer cable impedance.

- 2. The 0.3 pF capacitance is the parasitic capacitance of the tip resistor pads.

- 3. The equivalent series resistance is the sum of the tip resistor  $R_{tip}$  and the 120 $\Omega$  (dc component) logic analyzer cable impedance.

- 4. The capacitive load is the sum of the logic analyzer capacitance plus the T2 PCB transmission line lumped capacitance. Assuming T2 has a length of 1.4 inches and a 2 pF per inch capacitance, the equivalent capacitive load can be calculated by the following equation:

$C_{equiv}$  = 9 pF + T2<sub>pF/in</sub> x T2<sub>length</sub> = 9 pF + 2 pF/in x 1.4" = 11.8 pF

### **Extrapolating T1 and T2 Trace Lengths**

It is fairly straightforward to extrapolate the previous values for faster, slower, and intermediate rise times. For signals with rise times faster than 300 ps, a more detailed analysis must be performed. Refer to the following equations for calculating the optimal maximum trace length for the T1 and T2 PCB traces. Note that the following lengths are only approximations since the resistor values are selected to be compatible with industry standard components.

$$\begin{split} l_{\max} \approx \ t_{\text{rise time}} & \le 100 \ \text{ps} \ \text{max} < t_{\text{rise time}} \leq 750 \ \text{ps}, \ \text{R}_{\text{tip}} = 215\Omega \\ t_{\text{rise time}} > 750 \ \text{ps}, \ \text{R}_{\text{tip}} = 196\Omega \end{split}$$

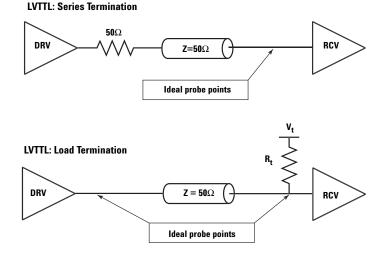

**Figure 5. LVTTL Series termination**

### **Routing Techniques**

Regardless of whether discrete networks are used or not, the following describes some general guidelines for probing high-speed signals and buses. LVTTL and SSTL logic buses are described here. *Note:*

The following schematics are meant to be a basic guide for probing placement, not a description of how to terminate transmission lines. Please refer to the vendors documentation for exact termination

#### Series Terminated LVTTL

techniques.

Series termination resistors can be used to dampen reflections on traces that exceed the length equals 1/5 rise time rule. Signals propagating along a source series transmission line resolve at the load. Midpoints along the transmission line will contain a partial signal rise until the reflection returns and completes the transition. If the intermediate step function voltage happens to be near the threshold voltage of the logic analyzer, metastability may occur and ultimately degrade setup and hold margins into the logic analyzer. Series terminated transmission lines should be probed at the load.

#### Load Terminated LVTTL

Uni-directional and bi-directional load terminated transmission lines can generally be probed at the driver, load, or anywhere in between as long as all signals are probed at the same position. It is important to keep the stub lengths less than 1/5 the rise time. Ideally, one endpoint should be selected for probing.

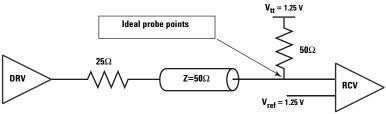

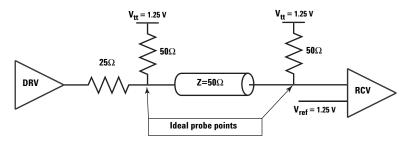

## SSTL-2

The Agilent SerDes drives/receives signals in an SSTL-2 format. While SSTL-2 provides excellent high-speed signal fidelity during transmission across a PCB board, issues arise that do not normally occur with single-ended LVTTL logic.

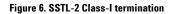

An SSTL-2 transmission line is shown in Figure 6. Class-I termination specifies a  $50\Omega$  resistor to Vtt at the receiver. Class-II termination requires a  $50\Omega$  resistor to Vtt at both the source and receiver. A  $25\Omega$  series resistor is typically designed into the driver. In general, it is safe to probe the signal at or very near the load termination resistors, which may be either end for Class-II buses.

## SSTL-3

The technique for termination and probing 3.3V SSTL logic is the same except the bias voltage is higher and the logic analyzer threshold must be set to 1.5V instead of 1.25V.

#### SSTL-2: Class-1 Termination

### SSTL-2: Class-II Termination

## **Logic Analyzer Connectors**

## **Mictor Connectors**

Mictor connectors are used to connect the SUT to the logic analyzer. The connectors each provide for 32 signals plus two clocks. The Mictor connectors each have 38 SMT pins plus five through-hole ground returns. Mechanical documentation and layout information can be found at www.agilent.com.

## **Connector Placement Techniques**

In general, connectors should be placed as close to the probe point as possible to minimize stubs. Refer to the section "Built-in termination Networks" page 3. for maximum recommended stub lengths. If discrete termination networks are used because of real estate concerns, connector placement typically becomes less critical since the maximum distance is effectively doubled. Traces from the termination networks should be matched in length so that all signals have equal propagation delays and setup and hold margins are preserved.

### **Mictor Connector Pinout**

Table 2 describes an example pinout for the Mictor-38 connector. Note that Agilent uses a staggered pin numbering (1 / 2 alternating sides) while other vendors may recommend numbering in order on one side. Either way, as long as the signals are routed to the correct physical location, the numbering scheme does not matter.

Agilent requires pins 1-4 to be left unconnected. In addition, the state analyzer clocks MUST be connected to pins 5 and 6. The 5 center plated mounting holes MUST be connected to ground. All other signals are user definable. Bused signals should place the MSB on pin 7/8, descending downward to the LSB.

Refer to the SerDes documentation for pin numbers.

| Odd Pin Side | Signal | Signal | Even Pin Side |

|--------------|--------|--------|---------------|

| 1            | NC     | NC     | 2             |

| 3            | NC     | NC     | 4             |

| 5            | CLKA   | CLKB   | 6             |

| 7            | DA[9]  | DB[9]  | 8             |

| 9            | DA[8]  | DB[8]  | 10            |

| 11           | DA[7]  | DB[7]  | 12            |

| 13           | DA[6]  | DB[6]  | 14            |

| 15           | DA[5]  | DB[5]  | 16            |

| 17           | DA[4]  | DB[4]  | 18            |

| 19           | DA[3]  | DB[3]  | 20            |

| 21           | DA[2]  | DB[2]  | 22            |

| 23           | DA[1]  | DB[1]  | 24            |

| 25           | DA[0]  | DB[0]  | 26            |

| 27           |        |        | 28            |

| 29           |        |        | 30            |

| 31           |        |        | 32            |

| 33           |        |        | 34            |

| 35           |        |        | 36            |

| 37           |        |        | 38            |

Table 2. Mictor-38 connectors for the Agilent SerDes

## Appendix

## Supported Logic Analyzer Modules for InfiniBand

InfiniBand applications should use model 16715A logic analyzer modules and higher. While the frequency of older logic analyzer modules may be sufficient, the eye-finder feature and better setup and hold window makes the 16715A and higher necessary.

| Agilent Part<br>Number | State Speed | Channels | Memory Depth         |

|------------------------|-------------|----------|----------------------|

| 16715/16A              | 167 MHz     | 68       | 2M State             |

| 16717A                 | 333 MHz     | 68       | 2M State             |

| 16750/51/52A           | 400 MHz     | 68       | 4M / 16M / 32M State |

| Agilent Part<br>Number | Description |          |                      |

| 16702B | Mainframe with display and touch-screen |

|--------|-----------------------------------------|

| 16700B | Mainframe with no display               |

| 16701B | Expansion Frame                         |

|        |                                         |

## **Probing Part Numbers and Ordering Information**

| Agilent Part | Description                                                 |  |  |

|--------------|-------------------------------------------------------------|--|--|

| Number       |                                                             |  |  |

| E5346-60001  | Set of 5 Mictor connectors for use with high-density cable  |  |  |

| E5346A       | High-density logic analyzer cable with built-in termination |  |  |

|              | networks                                                    |  |  |

| E5351A       | High-density logic analyzer cable with NO termination.      |  |  |

|              | Requires discrete termination.                              |  |  |

## **Related Literature**

| Publication<br>Number | Title                              | Description      |

|-----------------------|------------------------------------|------------------|

| 5968-4632E            | Probing Solutions for Agilent Tech | hnologies        |

|                       | Logic Analysis Systems             | Product Overview |

| 5968-9661E            | Agilent Technologies 16700 Series  | s Logic          |

|                       | Analysis System                    | Product Overview |

| 5988-2424EN           | Test Tools for InfiniBand          | Color Brochure   |

## **Technical Support**

Agilent Technologies Web Site: http://www.agilent.com/

Rambus is a trademark of Rambus, Inc.

#### **Agilent Technologies Warranty**

Agilent hardware products are warranted against defects in materials and workmanship for a period of one year from date of shipment. Some newly manufactured Agilent products may

contain remanufactured parts, which are equivalent to new in performance. If you send us a notice of such defects during the warranty period, we will either repair or replace hardware products that prove to be defective.

Agilent software and firmware products that are designated by Agilent for use with a hardware pr ductare warranted for a period of one year from date of shipment to execute their programming instructions when properly installed. If you send us notice of defects in materials or workmanship during the warranty period, we will repair or replace these products, so long as the defect does not result from buyer supplied hardware or interfacing. The warranty period is controlled by the warranty statement

#### Agilent Technologies' Test and Measurement Support, Services, and Assistance

Agilent Technologies aims to maximize the value you receive, while minimizing your risk and problems. We strive to ensure that you get the test and measurement capabilities you paid for and obtain the support you need. Our extensive support resources and services can help you choose the right Agilent products for your applications and apply them successfully. Every instrument and system we sell has a global warranty. Support is available for at least five years beyond the production life of the product. Two concepts underlie Agilent's overall support policy: "Our Promise" and "Your Advantage."

#### Our Promise

Our Promise means your Agilent test and measurement equipment will meet its advertised performance and functionality. When you are choosing new equipment, we will help you with product information, including realistic performance specifications and practical recommendations from experienced test engineers. When you use Agilent equipment, we can verify that it works properly, help with product operation, and provide basic measurement assistance for the use of specified capabilities, at no extra cost upon request. Many self-help tools are available.

#### Your Advantage

Your Advantage means that Agilent offers a wide range of additional expert test and measurement services, which you can purchase according to your unique technical and business needs. Solve problems efficiently and gain a competitive edge by contracting with us for calibration, extra-cost upgrades, outof-warranty repairs, and on-site education and training, as well as design, system integration, project management, and other professional engineering services. Experienced Agilent engineers and technicians worldwide can help you maximize your productivity, optimize the return on investment of your Agilent instruments and systems, and obtain dependable measurement accuracy for the life of those products.

## Agilent Email Updates

www.agilent.com/find/emailupdates Get the latest information on the products and applications you select.

www.agilent.com/find/agilentdirect Quickly choose and use your test equipment solutions with confidence.

#### Agilent T&M Software and Connectivity

Agilent's Test and Measurement software and connectivity products, solutions and developer network allows you to take time out of connecting your instruments to your computer with tools based on PC standards, so you can focus on your tasks, not on your connections. Visit **www.agilent.com/find/connectivity** for more information.

For more information about InfiniBand, log onto: www.agilent.com/find/InfiniBand By internet, phone, or fax, get assistance with all your test & measurement needs

**Phone or Fax**

United States: (tel) 800 829 4444

#### Canada:

(tel) 877 894 4414 (fax) 905 282 6495

#### China:

(tel) 800 810 0189 (fax) 800 820 2816

#### Europe:

(tel) (31 20) 547 2323 (fax) (31 20) 547 2390

#### Japan:

(tel) (81) 426 56 7832 (fax) (81) 426 56 7840

#### Korea:

(tel) (82 2) 2004 5004 (fax) (82 2) 2004 5115

#### Latin America:

(tel) (305) 269 7500 (fax) (305) 269 7599

#### Taiwan:

(tel) 0800 047 866 (fax) 0800 286 331

#### **Other Asia Pacific Countries:**

(tel) (65) 6375 8100 (fax) (65) 6836 0252 Email: tm\_asia@agilent.com

#### Online Assistance: ww.agilent.com/find/assist

Product specifications and descriptions in this document subject to change without notice.

© Agilent Technologies, Inc. 2005 Printed in USA, April 12, 2005

### 5988-2857EN