## A Bead Probe CAD Strategy for In-Circuit Test

Kenneth P. Parker Agilent Technologies Loveland, CO kenneth\_parker *at* agilent *dot* com

Don DeMille DeMille Research Inc. Lake Forest, CA Don\_DeMille *at* testsight *dot* com

## **Copyright © 2007 IEEE. Reprinted from 2007 ITC International Test Conference, Paper 18.2**

This material is posted here with permission of the IEEE. Such permission of the IEEE does not in any way imply IEEE endorsement of any of Agilent Technologies' products or services. Internal or personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution must be obtained from the IEEE by writing to pubs-permissions *at* ieee *dot* org.

By choosing to view this document, you agree to all provisions of the copyright laws protecting it.

# A Bead Probe CAD Strategy for In-Circuit Test

Kenneth P. Parker Agilent Technologies Loveland, CO kenneth\_parker *at* Agilent *dot* com

## Abstract

Bead Probe Technology has been developed as alternative In-Circuit Test (ICT) contact points replacing conventional test pads normally integrated into a printed circuit layout [Park04], [Park05], [DoGr06], [Agil07]. This paper discusses the potential of using Bead Probes in Computer Aided Design (CAD) systems when getting a board ready for production. It outlines the requirements that a software package must address in order to incorporate Bead Probes into the board design process. Finally, a software package was developed to implement this process and evaluations were made on a number of circuit boards representing the industry sectors of communications, consumer electronics, military/aerospace and automotive. The evaluations provide insight into the ability of Bead Probes to enhance access, manage board stress, reduce cost and increase ICT test reliability.

## 1 Bead Probe Overview

Bead Probe Technology (BPT) has been under study for several years now [Park04], [Park05] culminating in a High-Volume Manufacturing study [DoGr06] where over 1.5 million Beads were fabricated and measured under a multitude of conditions. Since then, several million more have been studied, fine tuning the process parameters needed to be successful with them. At this writing, several products are going into production using BPT [FaLe07].

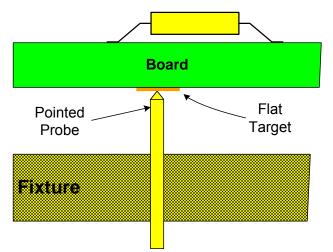

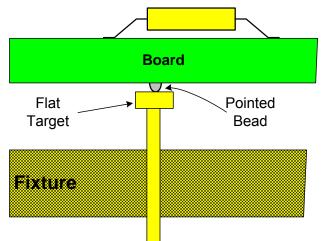

In a nutshell, BPT inverts the normal ICT access paradigm of placing test targets (or test pads) into a circuit layout that are then contacted by spring-loaded sharppointed spears in a test fixture. (See Figure 1.) In BPT, the test target is mounted in the test fixture, and the sharppointed object is mounted on the board. In this case, the object is a tiny, hemi-ellipsoidal Bead of solder fabricated atop a signal trace on the board as seen in Figure 2. This Bead contacts the fixture target probe during actuation of the fixture. While actuated, the spring-loaded fixture target probe is compressed into the rounded surface of the Bead which undergoes an engineered amount of plastic deformation. The deformation breaks the layer of oxide and contamination normally found on the surface of solder, giving excellent DC contact performance. Don DeMille DeMille Research Inc. Lake Forest, CA Don\_DeMille *at* testsight *dot* com

Figure 1: Conventional probing of a target in a board layout.

#### Figure 2: A fixture target probe contacting a Bead.

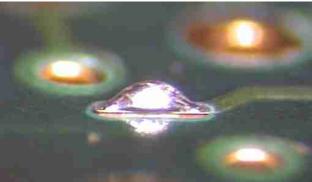

A photograph of a typical Bead Probe is shown in Figure 3. This Bead has not been contacted yet for test purposes, so it does not show any deformation. Once contacted, the top surface will be flattened a small amount due to plastic deformation, giving good contact impedance.

Beads will typically have a width dictated by the width of the trace upon which they sit. For wide traces,

say, greater than 6 mils, we restrain the Bead width to 6 mils. Thus, on wide traces and surface planes (such as power or ground) we can also construct Beads of similar size and properties. Ultimately, we could end up with test fixtures that are 100% BPT.

Figure 3: A Bead Probe, approximately 5 mils by 20 mils, viewed at a 30 degree angle.

Bead Probes have two very attractive properties that make them a desirable alternative:

- 1) they have negligible effect on the high-frequency performance of the circuit's intended design [Park04], [DoGr06] and

- 2) they have a "layout independent" placement property, meaning you can add them to a layout *after a design is completed* [Park05].

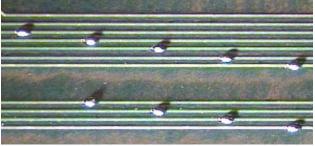

These two properties mean we can eliminate a lot of current negotiation that goes on between the design department and the test department. Many test points can be added to design layout after the fact without fear of changing circuit performance. (Note that since BPT is aimed at signals that appear on an outer layer, there may still be some negotiation about which signals make an appearance on the surface.) The photograph in Figure 4 shows a set of parallel signals traces with Beads added to them after the layout was complete.

Figure 4: Beads added to a parallel bus structure without layout modification.

The side-lighting used in this picture emphasizes (with shadows) how the Beads rise above the surface of the board. The spacing of these Beads is such that larger (cheaper) fixture target probes can be used in the test fixture, and this freedom of spacing can also be used to reduce board flex that may occur when too many springloaded probe forces are concentrated in a small area.

## 2 The Bead Design Process

Bead Probes are currently verified experimentally for circuit board traces and planes. (While Bead placement atop vias and micro-vias has been theorized, this has not yet been validated.) The following discussion focuses on Bead placement on traces. Power and ground plane Beads are useful for additional connectivity but have little impact on overall node access.

A software package intended for Bead Probes design must incorporate five basic functions:

- CAD Data import,

- Bead placement,

- soldermask modification,

- paste stencil modification, and

- merge mask and stencil bead data

An additional useful function is fixture probe placement as discussed below.

The first three steps are normally done by either the test engineer or the design engineer and occur before bare board fabrication.

The paste stencil modification must be done after the stencil materials, processes and thicknesses have been determined. This normally occurs just prior to the board fabrication process and probably will not include either the test or design engineer.

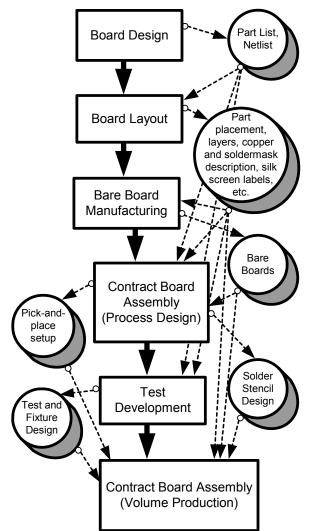

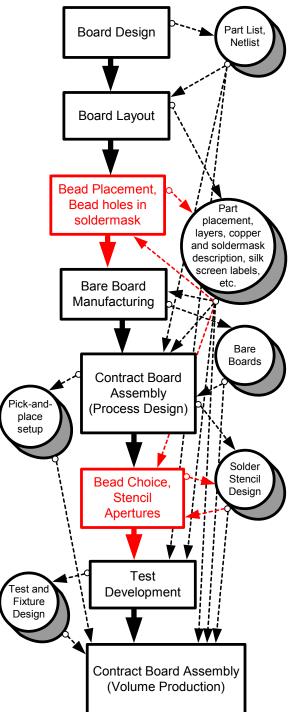

It is instructive to examine a (simplified) generic model of a board design-to-production model, as shown in Figure 5. This model utilizes standard In-Circuit testing without the use of Bead Probes, and assumes that board design is done independently of board production as is common with contract manufacturing widely in use today. Figure 6 then shows how this model is modified to account for the use of Bead Probe technology. The bold boxes show stages in the process, the round items show data, and dashed arrow lines show data flow. A key observation is that Bead Probe technology causes two changes; first in Bead placement, which will consequently cause modifications to the soldermask. Later, during manufacturing setup where the solder stencil design is finalized, aperture modifications are made to the stencil. The placement process is in lieu of layout modifications normally needed to provide test access, and can be done by a test engineer rather than the board designer. The stencil modifications feed off Bead placement data and can be performed by either the test engineer or the manufacturing setup engineer. Note these two engineers could be widely separated geographically and corporately.

## 2.1 CAD Transfer Data

CAD data comes from a variety of sources and formats. Most formats contain layout information including trace locations and widths. The Bead Probe implementation process starts with loading the CAD data for the circuit board. With reliable trace information, a software package, using the rules discussed below, can locate appropriate points on the traces to place a Bead Probe.

Figure 5: A typical board design-to-production flow without Bead Probes.

### 2.2 Bead Placement

The main goals when locating Beads on a circuit board are to minimize the potential for mechanical problems and maximize the potential for additional fixture probe locations. The main mechanical consideration is potential shorting due to misplaced Beads. Because Beads are being introduced after the design is complete, great care must be taken that no Beads create problems that would not exist without the Bead.

In the discussion below, 'Bead Probes' refer to the Beads placed on the circuit board, while 'fixture target probes' ('target probes') refer to the fixture-based spring loaded probe making contact with the circuit board Bead. The reason the fixture probe is the target was discussed in the overview above.

Before any Beads are placed, the Bead size for a

given trace must be defined. Next the spacing variables must be selected.

Figure 6: Board design-to-production flow when Bead Probe technology is utilized.

## 2.2.1 Defining Bead Sizes

Beads on a trace are defined by two values, the Bead width and an aspect ratio of Length to Width. An aspect ratio is used because Beads placed on traces below 6 mils in width are constrained by the trace width, so the designer only has the freedom to specify the length by adjusting the aspect ratio. These are called metal-defined Beads. For wider traces or planar areas, the designer has freedom to specify both the width and aspect ratio. These are called soldermask-defined Beads.

For both soldermask-defined and metal-defined Beads, a critical calculation is the spring force required to achieve the desired amount of deformation of the Bead as discussed above. The spring force is proportional to the solder yield strength and approximately proportional to the area of the Bead. Experimental results produced by Agilent (see also [DoGr06]) showed that spring forces of about 4 to 7 ounces (113 to 198 grams) are optimal for Beads, at least with off-the-shelf fixture probes, and with a 5000 lbs/inch<sup>2</sup> yield strength (352 kg/cm<sup>2</sup>) for typical lead-free solder alloys. This translates into an upper limit size on Beads of 6 mils (0.15 mm) with aspect ratio of 3 to 4, or 6x18 mils to 6x24 mils (0.15x0.48 mm to 0.15x0.61 mm).

Figure 7 shows an example Bead Definition dialog. Experimental results show that the aspect ratio of the bead should be reduced as the bead gets wider. In the table below, minimum and maximum trace widths (Min Trc, Max Trc) are defined up to 65 mils (1.65 mm). This is the upper limit for metal defined beads. Above 65 mils, the beads are solder mask defined with a fixed width of 6 mils and an aspect ratio of 3.

| , | Min Trc | Max Trc | Bead Width | Aspect | Max Spr |

|---|---------|---------|------------|--------|---------|

|   | 0.0025  | 0.0035  | Metal      | 5      | 2       |

|   | 0.0035  | 0.0045  | Metal      | 5      | 3.8     |

|   | 0.0045  | 0.0055  | Metal      | 4      | 5.1     |

|   | 0.0055  | 0.0065  | Metal      | 3.33   | 6.3     |

|   | 0.0065  | 0.05    | 0.006      | 3      | 6.8     |

Figure 7: Example of a setup dialog page for defining Bead Probe size attributes.

#### 2.2.2 Spacing Variables

When selecting a location on a trace to place a Bead, the closest distance from the Bead center to the closest edge of all other objects must at a minimum be the radius of the fixture target probe tip plus the maximum registration error. Figure 8 shows a "headless" fixture target probe designed for BPT.

However, if the closest object is another potential fixture probe target where the fixture probe tip radius can exceed the pad size, then the minimum spacing must be the maximum radius of any potential fixture probe tip, plus the registration error, plus one-half the Bead length. This situation can occur when the pad type is a thru-hole leg.

In general fixture probes intended for Beads will have headless flat tips that are smaller in diameter than conventional probes. An example of a Bead Spacing Dialog is shown in Figure 9. The Maximum Bead Probe Tip Diameter value of 36 mils (.91 mm) reflects the tip diameter of a commercially available fixture target probe seen in Figure 8.

Figure 8: A commercially available fixture target probe designed for Bead Probe use. (Courtesy QA Technology Company, Inc).

In placing the Bead Probes it is not necessary to worry about target probe drill sizes and spacing, since the fixture probe placement software will choose available Beads based on those rules, and ignore unused Beads.

When placing Beads, because of tight registrations on modern boards, the success of Bead placement is strongly dependant on the size of the values described above. It is important to minimize these values while insuring that sufficient margin exists for safety.

|   | Spacing                        | Value |

|---|--------------------------------|-------|

|   | Max Bead Probe Tip Diam        | 0.036 |

|   | Max Thru-Hole Leg Tip Diam     | 0.056 |

|   | To Part                        | 0.03  |

|   | From Corner(% of Length)       | 60    |

|   | Fixture Registration Error     | 0.005 |

| 1 | Solder Mask Registration Error | 0.003 |

## Figure 9: Example of a setup dialog page for defining Bead Probe spacing attributes.

In addition to the above spacing values, Bead Probes are automatically moved away from a trace corner by a percentage of the length of the Bead. This insures that the probe will not overrun the edge of the trace as it turns the corner. This "From Corner" value is expressed in percent of the Bead length.

Once the above conditions are met, Bead placement software should also try to maximize separations on a given trace. This allows maximum room for distribution of target probes.

## 2.2.3 Bead Keepouts

In addition to the spacing considerations, a candidate Bead point must be checked against the silkscreen layer to verify that no ink will be placed anywhere in the footprint of the Bead. Silkscreen ink can negatively impact the adhesion of the Bead to the trace.

Beads must also be kept out of some areas of the circuit board because of potential damage during selective wave-solder, or during rework with hot air knives or other tools.

## 2.2.4 The Placement Editor

The Placement Editor controls the side of the circuit board and the types of nets on which to place beads. Global settings provide control over the inclusion of noconnect and boundary scanned nets. Other settings determine the quantity of beads on a net and trace segment. Bead keepouts are also edited from this screen.

| NetType                         | Count | %    | ^ |

|---------------------------------|-------|------|---|

| Top Beads                       | 203   |      |   |

| Bottom Beads                    | 199   |      |   |

| All Nets, Exc NC: 4, Exc BS: 0  | 255   | 98.5 |   |

| Nets With Beads                 | 146   | 57.3 |   |

| ✓ Nets Without Beads            | 109   | 42.7 |   |

| Nets Without Beads And Probes   | 109   | 42.7 |   |

| Limited Access Nets With Beads  | 16    | 6.3  |   |

| Limited Access Nets Without Bea | 8     | 3.1  | ~ |

Figure 10: Example bead placement editor control screen.

## 2.2.5 Example Layout

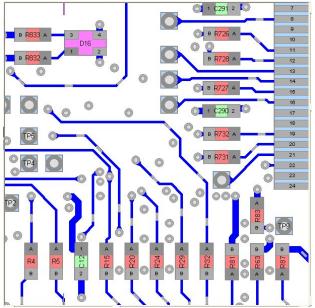

An example of a layout that was post-processed, upon design completion, to add Bead Probes, is shown in Figure 11

It shows a small portion of an outer plane of the layout. Each Bead Probe is indicated by the small, gray obround pattern seen on the blue nodes. Some nodes have multiple Bead Probe locations. Each could have a Bead fabricated, or, later processing could select the "best" Bead for each node and only utilize them and erase the rest. Erasure could amount to closing the stencil aperture for a Bead to be eliminated, or both the stencil aperture and the soldermask hole could be eliminated. However, since Beads have negligible effect on a board's functional performance, there is no harm in leaving the unused Beads in place. Doing so may actually facilitate later changes that may be needed for a layout and test fixture.

## 2.2.6 Soldermask Design

The soldermask shape is the same as the final intended bead shape. The only modification required is to provide an allowance for mask registration errors. Figure 12 shows a mask registration error with possibly insufficient overlap of the soldermask (light gray) to form a reliable bead.

Figure 11: Example of a layout that has been modifed (post design) to include Bead Probes. (Beads in gray).

Figure 12: Example of registration error. The soldermask is shown in light gray.

## 2.2.7 Paste Stencil Design

The paste stencil design depends on the stencil layer thicknesses, the paste material being used, and the transfer ratio of the paste to the board once the stencil is removed. This ratio varies with the print area ratio (PAR), which is the ratio of the area of the aperture itself divided by the area of the sidewalls of the aperture.

A table of experimentally derived data is used to determine the Transfer Ratio for a given PAR and technology. Figure 13 shows an example.

The target height for a bead is about one half of the bead width. The goal in the stencil design is to determine the size of the aperture opening that will result in placing exactly enough paste to achieve this target height.

Since aperture size depends on a ratio which changes with the aperture size, an algorithm that iterates to a solution is used to calculate the value of the Paste Stencil side (D).

| he | mically Etch | ed, Polished | - |

|----|--------------|--------------|---|

|    | PAR          | TR           |   |

| •  | 0.65         | 0.55         |   |

|    | 0.7          | 0.6          |   |

|    | 0.75         | 0.65         |   |

|    | 0.8          | 0.7          |   |

|    | 0.85         | 0.77         |   |

|    | 0.9          | 0.82         | - |

Figure 13: Table of measured Transfer Ratio values for a chemically etched and polished stencil.

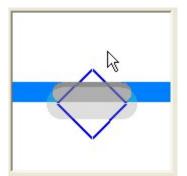

Figure 14 shows the resulting soldermask (light gray) and paste stencil (blue diamond) design for a metaldefined bead resting on a 5 mil (.127 mm) trace (solid blue horizontal line). The height value (2.547 mils or .065 mm) is the result of an iteration that terminates when it is within .05 mils (.001 mm) of optimum.

| Property               | Value   |  |

|------------------------|---------|--|

| Length                 | 20      |  |

| Width                  | 5       |  |

| Paste Mask Side (D)    | 12.5199 |  |

| Print Area Ratio (PAR) | 0.626   |  |

| Transfer Ratio (TR)    | 0.55    |  |

| Height                 | 2.5472  |  |

|                        |         |  |

|                        |         |  |

Figure 14: Example of metal-defined bead.

2.2.8 Merging the Solder Mask and Paste Stencil Bead Data.

The final step is to merge the new Bead mask modification into the existing soldermask and paste stencil layers. The board fabrication process then proceeds normally.

The most universal way to do this may be to merge the data back into the final Gerber output for the solder mask and paste stencil layers. Since the bead designs are single shapes that are called as flash (D03) points in the Gerber format, the bead data can be appended without affecting any of the original Gerber data. A mechanism to align the original Gerber with the new bead data is also necessary, since the CAD data used to design the beads may not have the same origin or rotation as the Gerber data.

## 3 Evaluating the Impact of Bead Probes in Production Test

DeMille Research developed software, based on its

TestSight Developer platform, integrating the Bead placement rules discussed above with fixture probe placement capabilities. This allows experiments to be conducted on a variety of boards to measure the affect on real world application of Bead Probes to traditional ICT problems.

## 3.1 Circuit Board Technology Groups

For these experiments, boards were selected to represent the broad technology segments of Military/Aerospace, Automotive, Consumer Electronics and Communications.

## 3.2 Industry Trends

Connecting reliably to traditional fixture probe targets is becoming more difficult [Rein05], [Rein06]. As via type pad sizes shrink below 25 mils (0.64 mm) on higher density boards, connectivity can begin to suffer to the point where false negative testing rates make probing the via undesirable, even if the added cost is not a factor. Some companies have already removed vias from the approved target list, eliminating a large source of contact opportunities and raising the question whether ICT is valid at all with the reduced access.

Lead-free coatings in some processes are causing some fixture designers to specify much higher probe forces to cut through the coatings. This adds stress to the board during test. By contrast, Bead Probes have a maximum spring force rating significantly lower than most traditional probes, at least when the tradition probes are fitted with higher force springs to reduce impedance. With Bead Probes, higher spring forces are undesirable and do not result in lower impedance connections beyond the upper recommended limit.

## 3.3 Evaluation Goals

Given the trends discussed above, these evaluations will look at Bead Probe impact in the key areas of overall fixture probe access, access without including via targets and force management.

## 3.4 General Assumptions

The fixture probe placement macro will not consider probes specified for centers closer than 50 mils (1.27 mm). In all evaluations no-connect nets (no electrical connection) are excluded from the net count. All evaluations assume top and bottom side probing, with the placement macro favoring bottom side probes

## 3.5 Setting the Variables

The maximum standard fixture thru-hole leg probe tip diameter considered is 56 mils (1.42 mm) and the maximum fixture target probe tip diameter is 36 mils (.91 mm). The circuit board registry error relative to fixture tooling pins is considered to be  $\pm$  -5 mils (0.13 mm).

Bead-to-pad separation is set to 25 mils (0.64 mm) which consists of a 20 mil (0.51 mm) tip radius plus the registration error.

The Bead-to-part separation is set to 30 mils (0.76

mm). This is the minimum part separation for a 50 mil (1.27 mm) fixture probe, so there is no advantage in a lower value.

### 3.6 Selecting the Circuit Boards

For the following experiments, a total of 22 boards were selected and categorized according to technology groups (6 each for Consumer and Communications, and 5 each for Automotive and Aerospace).

The circuit boards selected for evaluation were prescreened based on the percent of nets that have surface accessible traces, or about 10% of all boards looked at. Boards with large ground plane areas on the surface may not be good candidates for applying bead probes, unless vias are certified for bead probe placement.

## 4 Evaluation Experiments

## 4.1 Fixture Probe Access With Via Targets

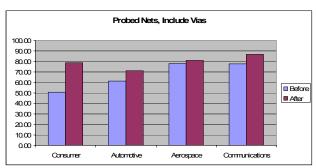

Chart 1: Probe access as a percent of total nets before and after adding bead probes. Includes via targets.

This evaluation summarized in Chart 1 looks at the percentage of probed nets before and after adding Beads, that is, first using conventional access including via, followed by adding Beads. The largest average increase in probed nets was 28% for consumer style boards, with increases of 10%, 3% and 9% respectively for Automotive, Aerospace and Communications boards. The maximum percent increase for a single board in each category was 56%, 54%, 7% and 26% respectively.

## 4.2 Fixture Probe Access Excluding Via Targets

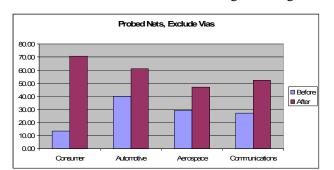

Chart 2: Probe access as a percent of total nets before and after adding bead probes. Excludes via targets.

This evaluation, summarized in Chart 2, looks at the

percentage of probed nets before and after adding beads without allowing conventional probing of any via targets. The largest increase in average nodal access was 57% for consumer style boards, and 20%, 18%, and 25% respectively for automotive, aerospace and communications boards. The maximum percent increase for a single board in each category was 79%, 43%, 36% and 41% respectively.

## 4.3 Force Management

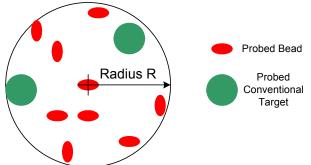

The Force Management evaluation calculates the maximum "spot force" and the overall force on a circuit board with and without Bead probes. In this study we used a simple first-order model for spot force by adding the force contributions of all probes in a standard 1 inch<sup>2</sup> (6.45 cm<sup>2</sup>) area (radius R = 0.564 inch or 1.43 cm) centered at one of the probes. See Figure 15. All beads were analyzed and the highest calculated spot force was recorded.

The general assumption for this evaluation is that conventional fixture probe spring forces will be about 2 ounces (57 grams) higher than fixture probes targeting Beads.

In order to normalize the data, lower spring force substitutions that might normally be made for force balancing are suppressed, and the total number of probes placed using beads was limited to the number without beads, that is, for nodes with multiple beads, only one was considered to be contributing force to the board.

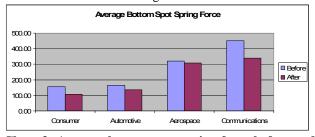

Chart 3: Average bottom spot spring force before and after beads. Includes via targets.

Chart 3 lists the average before and after spot spring forces for each of the board categories. Chart 4 lists the average percent decrease in total and spot forces as a

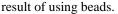

Chart 4: Percent decrease in bottom total and spot spring forces before and after beads. Includes via targets.

## 5 Conclusions

Chart 1 essentially shows the results of using beads to supplement traditional ICT fixture designs in which via targets are considered valid access points. The results are dramatically in favor of evaluating beads in the case of consumer style boards and incremental, on average, with the other three categories. However, individual boards within the remaining categories showed access improvements up to 56%.

The conclusion for traditional ICT design is that at a minimum, any board with a low probe access percentage should be evaluated for beads. Nearly every board in all categories will show some access improvement using beads.

Chart 2 shows the results of using beads on the emerging trend in ICT design of not allowing the use of via targets. The results are conclusive. Any company using this strategy should evaluate all boards for bead access. In many cases, absent an aggressive strategy to improve traditional test pad nodal access, a board will fall below an effective ICT test access threshold. In many cases, adding beads will bring the nodal access back to a point where ICT is viable.

The force management analysis shows an expected drop in overall spring force for each board category. The overall decrease in total force, as shown in Chart 4, was 38%, 14%, 4% and 12% respectively. This improvement comes without any loss in contact reliability.

The spot force percent decrease from Chart 3 is shown next to the total force decrease in Chart 4. We expect to see a higher spot than total percent decrease because the probe placement macro has additional targets to choose from in making the location selection. This proved true in the automotive and communications categories, and not true in the consumer and aerospace categories, although the spot decrease roughly tracked the total decrease.

In general, better force management is a free side effect of using bead probes. As the technology matures, even better results are to be expected.

In summary, bead probes are an important tool in

extending the effectiveness and longevity of ICT test. They should be considered an important part of any board test strategy.

## 6 Further Work

At the time of this writing, Bead Probe technology had not been qualified for application to vias or microvias. It is the authors' conviction that if Beads can be mounted on such "natural" test points, especially those too small for conventional probing, then access will yet again be greatly improved. It is also our thinking that the probing difficulties seen with conventional probing of vias will not occur when Beads are employed. This is because Bead are naturally convex structures, not concave, and will not be prone to collecting pools of hardened flux residue within them as can happen with vias.

We also invite further advanced study of board flex reduction. This can be done with finite element analysis and also with empirical strain-gauge measurements [LWH05]. With the freedom to add multiple alternative access points to many nodes, Beads can allow the wider distribution of probe access. This can both minimize board flex, and also allow the use of larger, cheaper fixture probes.

## 7 References

- [Agil07] "The Bead Probe Handbook", Agilent Technologies, 2007. Available to licensed Bead Probe Technology users, *http://www.agilent.com/see/beadprobe*

- [DoGr06] "Implementation of Solder-Bead Probing in High Volume Manufacturing", M. Doraiswamy and J. J. Grealish, *Proceedings, International Test Conference*, paper 5.4, Santa Clara CA, Oct 2006

- [FaLe07] "Implementing Bead Probe Technology for In-Circuit Test: A Case Study", M. Farrell and G. Leinbach, Proceedings IEEE International Test Conference, paper 18.1, Santa Clara CA, Oct 2007.

- [LWH05] "Board Strain States Method and FCBGA Mechanical Shock Analysis", F. Z. Liang, R. L. Williams and G. Hsieh, *Proceedings IMAPS Device Packaging Conference*, Scottsdale AZ, March 2005

- [Park04] "A New Probing Technique for High-Speed/High-Density Printed Circuit Boards", K. P. Parker, Proceedings IEEE International Test Conference, pp 365-374, Charlotte NC, Oct 2004

- [Park05] "Bead Probes in Practice", K. P. Parker, Proceedings IEEE International Test Conference, Paper 26.2, Austin TX, Nov 2005

- [Rein05] "Effect of Lead Free Solders on In-Circuit Test Process", R. D. Reinosa, *Proceedings, International Test Conference*, Paper 26.3, Austin TX, Nov 2005

- [Rein06] "Lead-free Through-Hole Technology (THT) and Contact Repeatibility in In-Circuit Test", R. D. Reinosa, *Proceedings, International Test Conference*, Paper 5.3, Santa Clara CA, Oct 2006

Product specifications and descriptions in this document subject to change without notice. (c) Agilent Technologies, Inc., 2008 Printed in USA, February 25, 2008 5989-8072EN