**APPLICATION NOTE 1003**

# Interfacing 18 Segment Displays to Microprocessors

## INTRODUCTION

Over the past four years, the need for alphanumeric displays has grown very rapidly due to the extensive use of microprocessors in new system designs. The HDSP-6508 and HDSP-6300 alphanumeric displays were developed to provide a low cost, easy-to-use alternative to 5x7 dot matrix displays. These displays use an 18 segment display font that includes a centered decimal point and colon for increased readability. This font is capable of displaying the 64 character ASCII subset (numbers, punctuation symbols, and upper case alphabet) as well as many special purpose symbols. The HDSP-6504 and HDSP-6508 are 3.81 mm (0.150") red 4 or 8 character displays in a dual-in-line package. The HDSP-6300 is a 3.56 mm (0.140") red 8 character display in a dual-in-line package. The HDSP-6508 has character-to-character spacing on 6.35 mm (0.250") centers while the HDSP-6300 has character-to-character spacing on 5.08 mm (0.200") centers. Paralleling the development of these alphanumeric displays have been the introduction of several new display interface circuits that simplify the use of the 18 segment display. These circuits include an ASCII to 18 segment decoder/driver and improved NPN Darlington digit drivers that are designed to interface directly to 5 volt digital logic. This Application Note deals with several techniques to interface the 18 segment display to microprocessor systems. Depending upon the overall system configuration, microprocessor time available to dedicate to display support, and the type of information to be displayed, the system designer would choose the best interface technique to drive an 18 segment display.

## **DISPLAY INTERFACE TECHNIQUES**

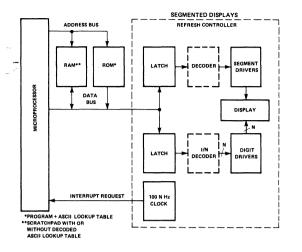

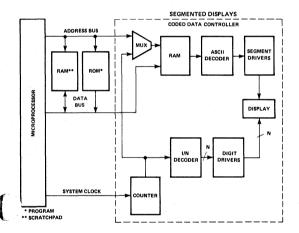

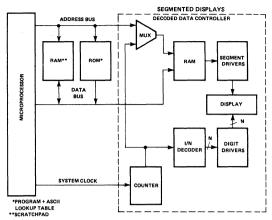

This application note will deal with four different techniques, as shown in Figure 1a-d, for interfacing the HDSP-6508 and HDSP-6300 displays to microprocessor systems.

The REFRESH CONTROLLER interfaces the microprocessor system to a multiplexed LED display. The controller periodically interrupts the microprocessor and after each interrupt, the microprocessor supplies new display data for the next refresh cycle of the display.

- 1b. The DECODED DATA CONTROLLER refreshes a multiplexed LED display independently from the microprocessor system. A local RAM stores decoded display data. This data is continuously read from the RAM and then used to refresh the display. Whenever the display message is changed, the microprocessor decodes each character in software and writes the decoded data into the local RAM.

- 1c. The CODED DATA CONTROLLER also refreshes a multiplexed LED display independently from the microprocessor system. The local RAM stores ASCII data which is continuously read from the RAM, decoded, and used to refresh the display. The display message is changed by writing new ASCII characters within the local RAM.

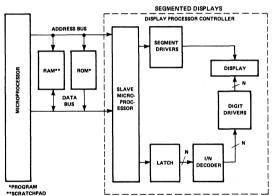

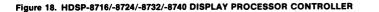

- 1d. The DISPLAY PROCESSOR CONTROLLER uses a separate microprocessor to drive the LED display. This microprocessor provides ASCII storage, ASCII decode, and display refresh independently from the main microprocessor system. Software within the dedicated microprocessor provides many powerful features not available in the other controllers. The main microprocessor updates the LED display by sending new ASCII characters to the slave microprocessor.

## COMPARISON OF INTERFACE TECHNIQUES

The choice of a particular interface is an important consideration because it affects the design of the entire microprocessor system. Each interface requires one or more memory or I/O addresses. These addresses are generated by decoding the microprocessor address bus. The display decoder can be located within the microprocessor program or as circuitry within the display interface. Location of the display decoder within the microprocessor program gives the designer total control of the display font within the program. This feature can be particularly important if the display will be used to display different languages and special graphics symbols. The interface technique chosen may limit or interfere with some programming techniques used in the rest of the microprocessor program. For example, the use of an

Figure 1d. DISPLAY PROCESSOR CONTROLLER Display Interface

interrupt may restrict the use of some programming techniques used in the interruptable portions of the microprocessor program.

The REFRESH CONTROLLER requires continuous interaction from the microprocessor system. Since the microprocessor actively strobes the LED display, the display interface circuitry is reduced. Generally, this technique provides the lowest hardware cost for any given display length. The display decoder can be located either within the microprocessor program or as circuitry within the interface. Display strobing is accomplished through use of the microprocessor time are directly proportional to display length. The DECODED DATA CONTROLLER and CODED DATA CONTROLLER require microprocessor interaction only when the display message is changed. Both techniques employ a local RAM memory that is continuously scanned by the display interface electronics. For the DECODED DATA CONTROLLER, the display decoder is located within the microprocessor software and the local RAM stores decoded display data. The CODED DATA CONTROLLER includes the display decoder within the display interface circuitry and the local RAM stores ASCII data. Since ASCII data is more compact than decoded display data, the CODED DATA CONTROLLER uses a smaller RAM than the DECODED DATA CONTROLLER. Both techniques allow the microprocessor to individually change each display character by a memory or I/O write to a specific display address. These interface techniques can accept new data at a very high rate.

The DISPLAY PROCESSOR CONTROLLER, like the previously defined CODED and DECODED DATA CONTROLLERS, requires microprocessor interaction only when the display message is changed. By using a dedicated microprocessor, the DISPLAY PROCESSOR CONTROLLER provides many additional display features. These features include multiple entry modes, a blinking cursor, editing commands, and a data output function. The software with the DISPLAY PROCESSOR CONTROLLER further reduces microprocessor interaction by providing more sophisticated data entry modes compared to the RAM entry mode provided by the DECODED DATA and CODED DATA CONTROLLERS. The display decoder can either be designed into the dedicated display microprocessor or can be located within a separate PROM. The use of a PROM allows the user to provide a special character font with additional circuitry. The DISPLAY PROCESSOR CONTROLLER does not allow as high a data entry rate as either the DECODED DATA or CODED DATA CONTROLLERS.

## **MICROPROCESSOR OPERATION**

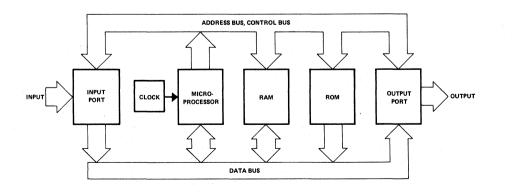

In order to effectively utilize the interface techniques outlined in the following sections, an understanding of microprocessor fundamentals is required. A brief description of microprocessor fundamentals is included in the following section. A microprocessor system usually consists of a microprocessor, ROM memory, RAM memory, and a specific I/O interface as outline in Figure 2. The microprocessor performs the desired system function by executing a program stored within the ROM. The RAM memory provides temporary storage for the microprocessor system. The I/O interface consists of circuitry that is used as an input to the system or as an output from the system. The microprocessor interfaces to this system through an address bus, data bus, and control bus. The address bus consists of several outputs  $(A_0, A_1, ..., A_n)$  from the microprocessor which collectively specify a binary number. This number or "address" uniquely specifies each word in the ROM memory, RAM memory, and I/O interface. The data bus serves as an input to the microprocessor during a memory or input read and as an output from the microprocessor during a memory or output write. The control bus provides the required timing and signals to the microprocessor system to distinguish a memory read from a memory write, and in some systems an I/O read from an I/O write. These control lines and the timing between the address bus, data bus, and control bus vary for different microprocessors.

The address, data, and control buses provide the flow of instructions and data into the microprocesor. Program execution consists of a series of memory reads (instruction fetches) which are sometimes followed by a memory read or write (instruction execution). The microprocessor performs a memory read by outputting the memory address of the word to be read on the address bus. This address uniquely specifies a word within the memory system. The microprocessor also outputs a signal on the control bus, which instructs the memory system to perform a memory read. The address selects one memory element, either RAM or ROM, within the memory system. Then, the desired word within the selected memory element is gated on the data bus by the read signal. Meanwhile, the unselected memory elements tristate their output lines so that only the selected memory element is active on the data bus. After sufficient delay, the microprocessor reads the word that appears on the data bus. Similarly, for a memory write, the microprocessor outputs the memory address of the word to be written on the address bus. After sufficient delay, the microprocessor outputs a signal on the control bus, which instructs the memory system to perform a memory write.

Figure 2. Block Diagram of a Typical Microprocessor System

The microprocessor also outputs the desired memory word on the data bus. The address selects one RAM memory element within the memory system. The write signal causes the memory element to read the word on the data bus and store it at the desired location. After the write cycle has been completed, the new word will have replaced the previous word within the RAM memory. During the memory write, outputs from the unselected memory elements remain tristated so that only the microprocessor is active on the data bus. These control lines and the timing for the address bus, data bus, and control bus vary for different microprocessors.

Some microprocessors, such as the Motorola 6800 microprocessor family, handle memory and I/O in exactly the same way. Memory and I/O occupy a common address space and are accessed by the same instructions. With this type of microprocessor, the hardware decoding of the address bus determines whether the read or write is to a memory or I/O element. Other microprocessors, such as the Intel 8080A, Intel 8085A, and the Zilog Z-80 have separate address spaces for memory and I/O. These microprocessors use different instructions for a memory access or an I/O access and provide signals on the control bus to distinguish between memory and I/O. One advantage of this approach is that the I/O address space can be made smaller to simplify device decoding. However, the I/O instructions that are available are usually not as powerful as the memory reference instructions. Of course, the user can always locate specific I/O devices within the memory address space through proper decoding of the address and control buses. This would allow these I/O devices to be accessed with memory reference instructions.

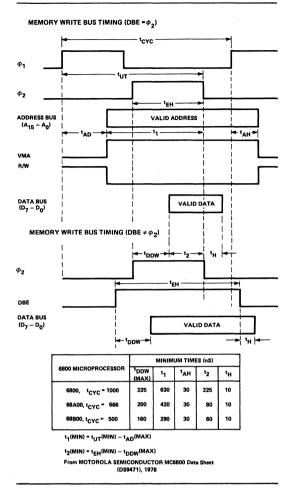

The 6800 microprocessor family has a 16 line address bus, 8 line data bus, and a control bus that includes the signals VMA (Valid Memory Address), R/W (Read/Write), DBE (Data Bus Enable), and clock signals  $\phi_1$  and  $\phi_2$ . R/W specifies either a memory read or write while VMA is used in conjunction with R/W to specify a valid memory address. DBE gates the internal data bus of the 6800 to the external data bus. In many applications, DBE is connected to  $\phi_2$ . Additional data hold time, t<sub>H</sub>, can be achieved by delaying  $\phi_2$  to the microprocessor or by extending DBE beyond the falling edge of  $\phi_2$ . The timing between the address bus, data bus, VMA, and R/W for a memory write is shown in Figure 3.

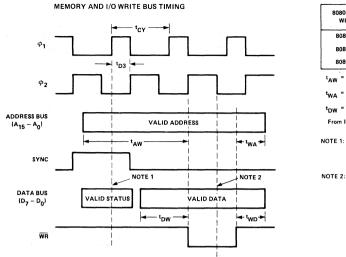

For the 8080A microprocessor, the address bus consists of 16 lines, the data bus consists of 8 lines, and the control bus consists of several lines including DBIN (Data Bus In), WR (Write), SYNC (Synchronizing Signal), READY, and clock signals  $\phi_1$  and  $\phi_2$ . DBIN and WR are used to specify a read or write operation. The 8080A microprocessor distinguishes memory from I/O through the use of a status word that precedes every machine cycle. When SYNC is high, the status word should be loaded into an octal latch on the positive edge of  $\phi_1$ . The outputs from the latch can then be decoded to specify whether the machine cycle is a memory write, memory read, I/O write, or I/O read. The Intel 8228 or 8238 System Controller provides this status latch and additionally encodes the outputs of the status latch with DBIN and WR to generate four timing signals MEM R (Memory Read), MEM W (Memory Write), I/O R (I/O Read), and I/O W (I/O Write). However, the 8228 and 8238 do not provide the outputs of the status latch. The timing between the address bus, data bus, WR, and SYNC

for both a memory write and an I/O write is shown in Figure 4. The 8080A also provides an input, READY, which allows the memory system to extend the time the address and data bus is valid by integral clock cycles.

## **REFRESH CONTROLLERS**

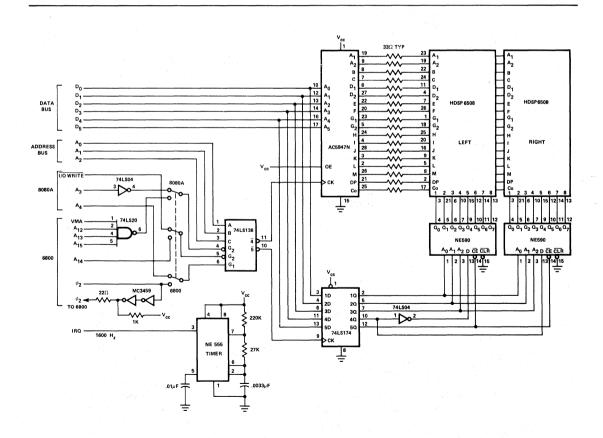

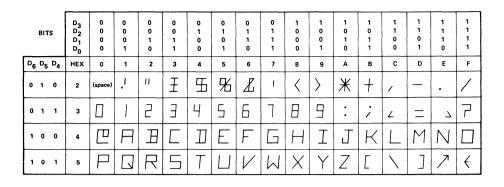

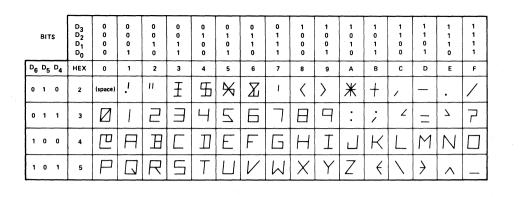

Figure 5 shows a REFRESH CONTROLLER for a 16 character 18 segment alphanumeric display. The circuit operates by interrupting the microprocessor at a 1600 Hz rate. Following each interrupt, the microprocessor responds by outputting a new ASCII character to the Texas Instruments AC5947 ASCII to 18 Segment Decoder/Driver and a new digit word to the 74LS174. The character font for the AC5947 is shown in Figure 6. The outputs of the 74LS174 are decoded such that digit word 00<sub>16</sub> turns the leftmost display character on, digit word 0F<sub>16</sub> turns the rightmost display character on, and digit word 1F<sub>16</sub> turns all digits off. The interface can be expanded to 24 characters with an additional Signetics NE590 driver. This change would also require modifications in IF peak, and the interrupt rate.

| 8080 MICROPROCESSOR            | MINIMUM TIMES (nS) |     |                 |                 |  |  |

|--------------------------------|--------------------|-----|-----------------|-----------------|--|--|

| WITH 8228 CLOCK                | tAW                | twA | <sup>t</sup> DW | <sup>t</sup> wD |  |  |

| 8080A, t <sub>CY</sub> = 480   | 740                | 90  | 230             | 90              |  |  |

| 8080A-2, t <sub>CY</sub> = 380 | 560                | 80  | 140             | 80              |  |  |

| 8080A-1, t <sub>CY</sub> = 320 | 470                | 70  | 110             | 70              |  |  |

$t_{AW} = 2t_{CY} - t_{D3} - [140(A), 130(A-2), 110(A-1)]$

$t_{WA} = t_{WD} = t_{D3} + 10$

$t_{DW} = t_{CY} - t_{D3} - [170(A), 170(A-2), 150(A-1)]$

From INTEL Component Data Catalog, 1978

- NOTE 1: Status Word should be loaded into an octal latch when SYNC = 1 on positive edge of  $\phi_1$ .

- NOTE 2: Additional wait cycles can be inserted here. A wait cycle is added by forcing READY low prior to the falling edge of  $\varphi_2$  during the clock cycle preceeding the falling edge of WR.

Figure 4. Memory and I/O Write Timing for the Intel 8080A Microprocessor Family

Figure 5. 6800 or 8080A Microprocessor Interface to the HDSP-6508 REFRESH CONTROLLER Utilizing the Texas Instruments AC5947 ASCII to 18 Segment Decoder/Driver

#### Figure 6. 18 Segment Display Font for the Texas Instruments AC5947 ASCII to 18 Segment Decoder/Driver

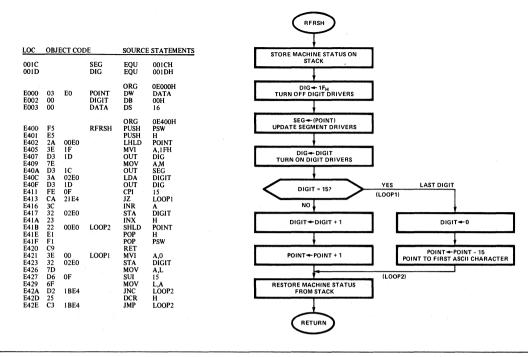

A 6800 microprocessor program that interfaces to this REFRESH controller is shown in Figure 7. Following each interrupt, the program "RFRSH" is executed. The program uses a scratch pad register "POINT" that points to the location within a 16 byte ASCII message of the next ASCII character to be stored in the display interface. The scratch pad register "DIGIT" contains the next digit word to be loaded into the display interface. The program interfaces to the circuit through two memory or I/O addresses. A memory write to address "SEG" writes a six bit word into the AC5947, and a memory write to address "DIG" writes a five bit word into the 74LS174. To prevent undesirable ghosting, the digit drivers are turned off prior to loading the next ASCII character into the AC5947. After sufficient delay, the next digit is turned on. Registers "POINT" and "DIGIT" are then updated by the program. Following execution of the "RTI" instruction, execution of the main program is resumed. A similar program written for an 8080A microprocessor is shown in Figure 8. The 6800 microprocessor program shown in Figure 7 operated with a 1 MHz clock requires 0.11% + 0.72n% of the available microprocessor time to refresh the display at a 100 Hz refresh rate, where n is the display length. The 8080A microprocessor program shown in Figure 8 when operated with a 2 MHz clock requires 0.31% + 0.96n% of the available microprocessor time to refresh the display at a 100 Hz refresh rate, where n is the display length. For example, the 16 character display shown in Figure 5

|                                              |                                          |                                |                        |                                                |                                                      | RFRSH                                           |                                                     |

|----------------------------------------------|------------------------------------------|--------------------------------|------------------------|------------------------------------------------|------------------------------------------------------|-------------------------------------------------|-----------------------------------------------------|

| LOC                                          | OBJ                                      | ECT CO                         | DE                     | SOURCE                                         | E STATEMENTS                                         |                                                 |                                                     |

|                                              | BF0<br>BF0                               |                                | SEG<br>DIG             | EQU<br>EQU                                     | \$BF04<br>\$BF05                                     | DIG ← 1F <sub>H</sub><br>TURN OFF DIGIT DRIVERS |                                                     |

| 0000<br>0002<br>0003                         | 000:<br>00                               | 3                              | POINT<br>DIGIT<br>DATA | FDB<br>FCB<br>RMB                              | DATA<br>0<br>16                                      | SEG ← (POINT)<br>UPDATE SEGMENT DRIVERS         |                                                     |

| 0400<br>0400<br>0402<br>0404<br>0406<br>0409 | DE<br>E6<br>86<br>B7<br>F7               | 00<br>00<br>1F<br>BF05<br>BF04 | RFRSH                  | ORG<br>LDX<br>LDA B<br>LDA A<br>STA A<br>STA B | \$0400<br>D,POINT<br>X,0<br>I,\$1F<br>E,DIG<br>E,SEG | A ← DIGIT                                       |                                                     |

| 040C<br>040E<br>0410<br>0412<br>0415<br>0416 | 96<br>81<br>27<br>7C<br>08<br><b>B</b> 7 | 02<br>0F<br>0A<br>0002<br>BF05 |                        | LDA A<br>CMP A<br>BEQ<br>INC<br>INX<br>STA A   | D,DIGIT<br>1,15<br>LOOP1<br>E,DIGIT<br>E,DIG         | A = 15?                                         | YES LAST DIGIT<br>(LOOP1)                           |

| 0419<br>041B<br>041C                         | DF<br>3B<br>7F                           | 00<br>0002                     | LOOPI                  | STX<br>RTI<br>CLR                              | D,POINT<br>E,DIGIT                                   | DIGIT ← DIGIT + 1                               | DIGIT ← 0                                           |

| 041F<br>0422<br>0425<br>0427<br>0429         | F6<br>B7<br>C0<br>D7<br>24               | 0001<br>BF05<br>0F<br>01<br>03 |                        | LDA B<br>STA A<br>SUB B<br>STA B<br>BCC        | E,POINT+1<br>E,DIG<br>I,15<br>D,POINT+1<br>LOOP2     | POINT ← POINT + 1                               | POINT ~ POINT - 15<br>POINT TO FIRST ASCII CHARACTE |

| 042B<br>042E                                 | 7A<br>3B                                 | 0000                           | LOOP2                  | DEC<br>RTI                                     | E,POINT                                              | DIG ← A<br>TURN ON SEGMENT DRIVERS              | UIG ← A<br>TURN ON SEGMENT DRIVERS                  |

|                                              |                                          |                                |                        |                                                |                                                      | RETURN                                          | RETURN                                              |

Figure 7. 6800 Microprocessor Program and Flowchart that Interfaces to the REFRESH CONTROLLER Shown in Figure 5

Figure 8. 8080A Microprocessor Program and Flowchart that Interfaces to the REFRESH CONTROLLER Shown in Figure 5

requires 11.6% of the 6800 microprocessor time or 15.7% of the 8080A microprocessor time to refresh the display at a 100 Hz refresh rate. Faster versions of the 6800 and 8080A microprocessors can reduce this microprocessor time by 50%.

# **DECODED CONTROLLERS**

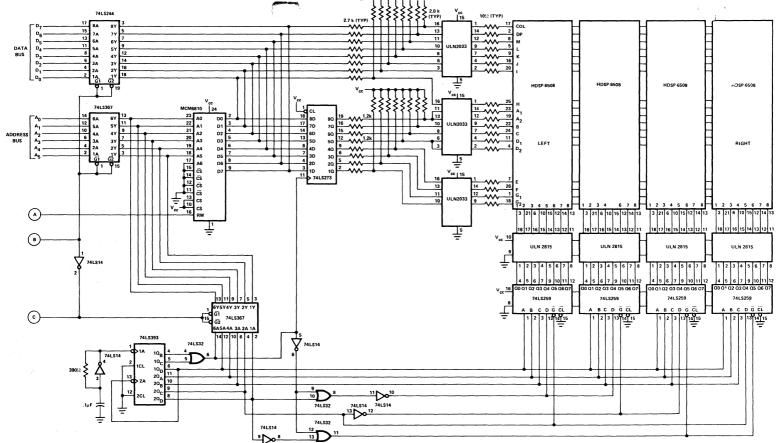

Figure 9 shows a DECODED DATA CONTROLLER designed for a 32 character 18 segment alphanumeric display. To simplify the circuitry, the display is configured as a 14 segment display with decimal point and colon. This allows each display character to be specified by two 8 bit words. One possible display font is shown in Figure 10. The Motorola 6810 RAM stores 64 bytes of display data that are continually read and displayed. The display data is organized within the RAM such that addresses A5, A4, A<sub>3</sub>, A<sub>2</sub>, and A<sub>1</sub> specify the desired character and address An differentiates between the two words of display data for each character. The display data is formatted such that word 0 (D7-D0) is decoded as G2, G1, F, E, D, C, B, and A; and word 1 (D7-D0) is decoded as COLON, DP, M, L, K, J. I, and H. The display data is coded low true such that a low output turns the appropriate segment on. Strobing of the display is accomplished with the 74LS14 oscillator and 74LS393 counter. The counter continuously reads display data from the RAM and enables the appropriate digit driver. The time allotted to each digit is broken into four segments. During the first segment of time, the display is turned off and work 0 is read from the RAM and stored in the 74LS273 octal register. During the next three segments of time, word 1 is read from the RAM and the display is turned on. Thus, the display duty factor is (1/32)

(3/4) or 1/42.6. For values of R and C specified, the display is strobed at a 130 Hz refresh rate.

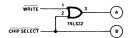

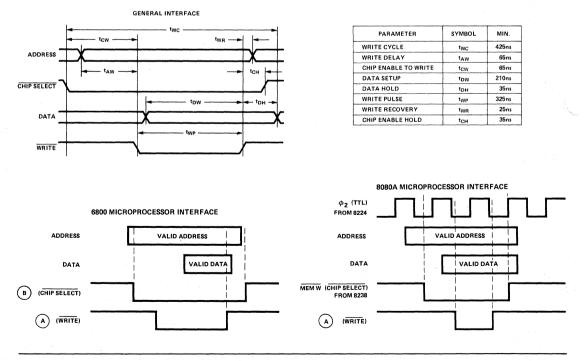

Data is entered into the RAM from the address and data bus of the microprocessor via two control lines, Chip Select and Write. When Chip Select goes low, the address generated by the counter is disabled and the microprocessor address and data bus is gated to the RAM. Then, after sufficient delay, the Write input is pulsed. which stores the data within the RAM. The data entry timing for the 18 segment DECODED DATA CON-TROLLER is shown in Figure 11. Because of the requirement that the address inputs of the 6810 RAM must be stable prior to the falling edge of Write, Chip Select should go low for time tow prior to the falling edge of Write. To guarantee that the address and data inputs of the RAM remain stable until after Write goes high, Chip Select should remain low for time ton following the rising edge of Write. This requirement for two separate timing signals is also required for the CODED DATA CONTROLLER shown in Figure 15. Because this interface timing is somewhat more difficult than the previously described circuits, the following methods are presented for interfacing to commonly used microprocessors.

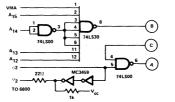

Interface to the 6800 microprocessor family is accomplished by NANDing together VMA and some specified combination of high order address lines to generate Chip Select and using  $\phi_2$  to generate Write.

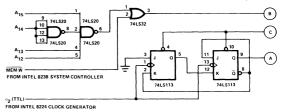

For the 8080A and 8085A microprocessor families, the limited flexibility of the output instruction requires that the 18 segment DECODED DATA CONTROLLER must be addressed as memory instead of I/O. The 8080A micro-

GENERAL INTERFACE

6800 MICROPROCESSOR INTERFACE

8080A MICROPROCESSOR INTERFACE (UTILIZING 8233 SYSTEM CONTROLLER)

Figure 9. 6800, 8080A, and General Interface to the HDSP-6508 DECODED DATA CONTROLLER

437

Figure 10. One Possible 16 Segment Display Font (14 Segments Plus Decimal Point and Colon) for the DECODED DATA CONTROLLER Shown in Figure 9.

processor requires an external status latch to hold status information provided during program execution. This status latch function can be implemented with an octal register such as the Intel 8212 or 74LS273. A Memory Write signal can be generated by NORing together all outputs of this status latch. This signal can then be NANDed with some specified combination of high order address lines to generate Chip Select. The 8080A WR output can then be connected to Write. The Intel 8238 System Controller, which is commonly used with the 8080A microprocessor, prevents direct access to the outputs of the status latch. An example of an interfacing to a system utilizing the 8238 is illustrated in Figure 9. MEM W from the 8238 is inverted and then NANDed with some specified combination of high order address lines to generate Chip Select. The 74LS113 generates Write from the microprocessor clock,  $\phi_2$  (TTL).

Interface to the 8085A microprocessor family can be accomplished by inverting the I/O/M output and NANDing the resulting signal with the S<sub>0</sub> output and some specified <u>combination</u> of high order address lines to generate Chip Select. The WR output from the microprocessor is connected directly to Write.

Figure 11. Data Entry Timing for the DECODED DATA CONTROLLER Shown in Figure 9

Figure 12. 6800 Microprocessor Program and Flowchart that Interfaces to the DECODED DATA CONTROLLER Shown in Figure 9

The simplest interface to the Z-80 microprocessor family is accomplished by addressing the 18 segment DE-CODED DATA CONTROLLER as I/O instead of memory. An example of this interface is shown in Figure 15. The IORQ output is inverted and NANDed with some specified combination of address lines to generate Chip Select. The 74LS113 circuit generates Write from the inverted microprocessor clock  $\phi$ .

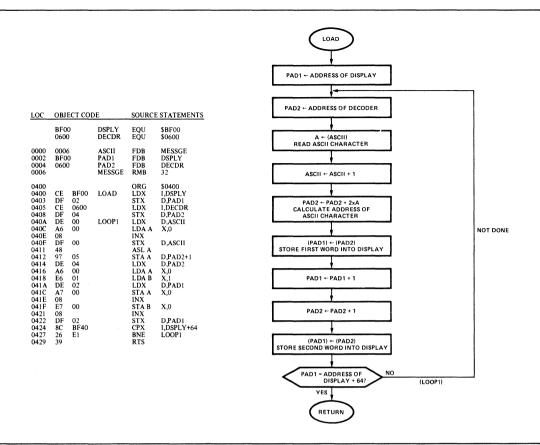

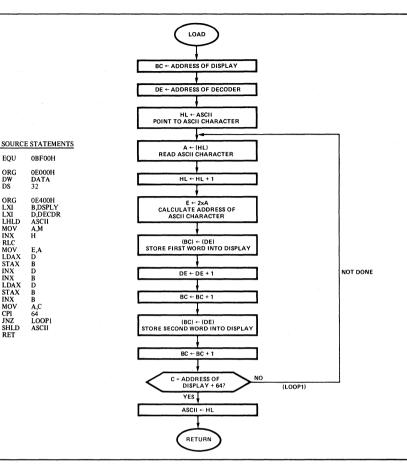

A 6800 microprocessor program that interfaces to the 18 segment DECODED DATA CONTROLLER is shown in Figure 12. This program decodes 32 ASCII characters and stores the resulting decoded display data within the display. The scratch pad register "ASCII" points to the location of the next ASCII character to be decoded. The program reads the first ASCII character, increments the point, "ASCII," and then looks up two words of display data within the 64 character ASCII look-up table "DECDR." These words of display data are then stored at the two addresses for the leftmost display location. Subsequent ASCII characters are decoded, and stored at the appropriate address within the display until all 32 characters have been decoded. After the program is finished, the pointer "ASCII" will have been incremented by 32. This program requires 2.4 ms for a 1 MHz clock to decode and load 32 ASCII characters into the 18 segment DECODED DATA CONTROLLER. The corresponding 8080A microprocessor program is shown in Figure 13. This program requires 1.4 ms for a 2 MHz clock to decode and load 32 ASCII characters into the 18 segment DECODED DATA CONTROLLER.

The 64 character ASCII font shown in Figure 10 can be generated using the table shown in Figure 14. This ASCII decoder uses two 8 bit words to represent each ASCII character. The format of the decoder is consistent with either the 6800 microprocessor program shown in Figure 12 or the 8080A microprocessor program shown in Figure 13.

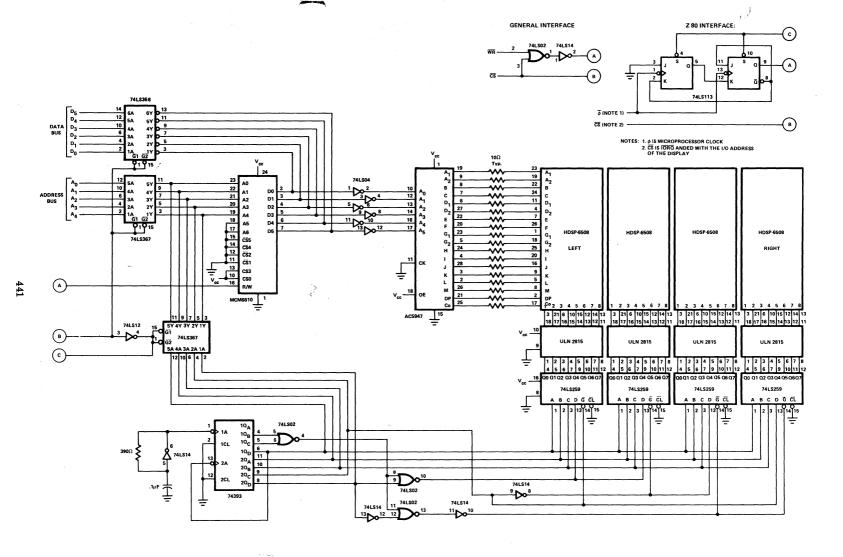

# CODED DATA CONTROLLERS

Figure 15 shows a CODED DATA CONTROLLER designed for a 32 character 18 segment alphanumeric display. Operation of this circuit is similar to the DECODED DATA CONTROLLER shown in Figure 9 except that the Motorola 6810 RAM stores 32 six bit ASCII words and the Texas Instruments AC5947 decodes this ASCII data into 18 segment display data. The resulting display font is shown in Figure 6. Strobing of the display is accomplished by the 74LS14 oscillator and 74LS393 counter. Because the long propagation delay through the AC5947 tends to cause display ghosting, the display is

Figure 13. 8080A Microprocessor Program and Flowchart that Interfaces to the DECODED DATA CONTROLLER Shown in Figure 9

LOC

**BF00**

E000 E002 02 00 E0

E400 E403 E406 E409 E404 E409 E408 E400 E400 E400 E400 E400 E411 E412 E413 E414 E415 E415 E41A E41D 01 11 2A 7E 23 07 5F 1A 02 13 03 1A 02 03 79 FE C2 22 C9

OBJECT CODE

00BF 00E5 00E0

40 09E4

00E0

DSPLY

ASCII DATA

LOAD

LOOPI

EQU

ORG DW DS

ORG

LXI LXI LXI LHLD MOV INX RLC MOV LDAX STAX INX INX INX INX INX MOV CPI JNZ SHLD RET

| ASCII | SYMBOL  | WORD 0 | WORD 1 |   |  | ASCII | SYMBOL           | WORD 0 | WORD 1 |

|-------|---------|--------|--------|---|--|-------|------------------|--------|--------|

| 20    | (SPACE) | FF     | FF     | - |  | 40    | æ                | 44     | FD     |

| 21    | ;       | FF     | BD     |   |  | 41    | Ă                | 08     | FF     |

| 22    | "       | DF     | FD     |   |  | 42    | В                | 70     | ED     |

| 23    | #       | 36     | ED     |   |  | 43    | ē                | C6     | FF     |

| 24    | #<br>\$ | 12     | ED     |   |  | 44    |                  | FO     | ED     |

| 25    | %       | 1B     | D2     |   |  | 45    | D<br>E<br>F      | 86     | FF     |

| 26    | &       | F2     | CA     |   |  | 46    | F                | 8E     | FF     |

| 27    | ,       | FF     | FD     |   |  | 47    | G                | 42     | FF     |

| 28    | (       | FF     | F3     |   |  | 48    | н                | 09     | FF     |

| 29    | j       | FF     | DE     |   |  | 49    | I                | F6     | ED     |

| 2A    | *       | 3F     | CO     |   |  | 4A    | J                | El     | FF     |

| 2B    | +       | 3F     | ED     |   |  | 4B    | ĸ                | 8F     | F3     |

| 2C    | ۰,      | FF     | DF     |   |  | 4C    | L                | C7     | FF     |

| 2D    | -       | 3F     | FF     |   |  | 4D    | М                | C9     | FA     |

| 2E    |         | FF     | BF     |   |  | 4E    | N                | C9     | F6     |

| 2F    | /       | FF     | DB     |   |  | 4F    | 0                | CO     | FF     |

| 30    | 0       | CO     | DB     |   |  | 50    | Р                | OC     | FF     |

| 31    | 1       | FF     | ED     |   |  | 51    | Q                | CO     | F7     |

| 32    | 2       | 24     | FF     |   |  | 52    | Q<br>R<br>S<br>T | OC     | F7     |

| 33    | 23      | 30     | FF     |   |  | 53    | S                | 12     | FF     |

| 34    | 4       | 19     | FF     |   |  | 54    | Т                | FE     | ED     |

| 35    | 5       | 96     | F7     |   |  | 55    | U                | C1     | FF     |

| 36    | 6       | 02     | FF     |   |  | 56    | v                | CF     | DB     |

| 37    | 7       | F8     | FF     |   |  | 57    | W                | C9     | D7     |

| 38    | 8       | 00     | FF     |   |  | 58    | X                | FF     | D2 -   |

| 39    | . 9     | 18     | FF     |   |  | 59    | Y                | FF     | EA     |

| 3A    | :       | FF     | 3F     |   |  | 5A    | Z                | F6     | DB     |

| 3B    | ;       | FF     | 5F     |   |  | 5B    | 1                | 7F     | F3     |

| 3C    | <       | 7F     | FB     |   |  | 5C    | Ń                | FF     | F6     |

| 3D    | =       | 37     | FF     |   |  | 5D    | 1                | BF     | DE     |

| 3E    | >       | BF     | FE     |   |  | 5E    | · ·              | FF     | D7     |

| 3F    | ?       | 7C     | EF     |   |  | 5F    | 1.1.1.1.1.1      | F7     | FF     |

|       |         |        |        |   |  |       |                  |        |        |

|       |         |        |        |   |  |       |                  |        |        |

Figure 14. 64 Character ASCII Decoder Table for the Microprocessor Programs Shown in Figures 12 and 13. 18 Segment Display Font is Shown in Figure 10.

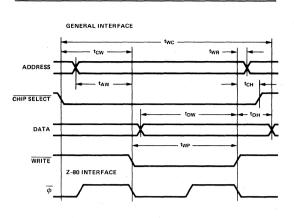

Figure 15. General Interfaces to the HDSP-6508 CODED DATA CONTROLLER

| PARAMETER            | SYMBOL | MIN.  |

|----------------------|--------|-------|

| WRITE CYCLE          | twc    | 455ns |

| WRITE DELAY          | tAW    | 65ns  |

| CHIP ENABLE TO WRITE | tcw    | 65ns  |

| DATA SETUP           | tow    | 215ns |

| DATA HOLD            | tDH    | 50ns  |

| WRITE PULSE          | twp    | 340ns |

| WRITE RECOVERY       | twn    | 40ns  |

| CHIP ENABLE HOLD     | tсн    | 50ns  |

|                      |        |       |

blanked momentarily after each new character is read from the RAM. This is accomplished by breaking the total time allotted for each digit into four segments. During the first segment, the display is turned off to allow data to ripple through the AC5947 and during the next three segments, the display is turned on. The resulting display duty factor is (1/32) (3/4) or 1/42.6. The display is strobed at a 130 Hz refresh rate.

Data is entered into the RAM from the address and data bus of the microprocessor via two control lines Chip Select and Write. When Chip Select goes low, the address from the counter is tristated and the microprocessor address bus and data bus is gated to the RAM. Then after sufficient delay, the Write input is pulsed, which stores the data within the RAM. Data entry timing for the 18 segment CODED DATA CONTROLLER is shown in Figure 16. Since this timing is very similar to the DECODED DATA CONTROLLER shown in Figure 9, interface to the various microprocessor families is the same as described in the section on DECODED DATA CONTROLLERS.

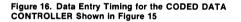

## DISPLAY PROCESSOR CONTROLLERS

The DISPLAY PROCESSOR CONTROLLER provides a powerful, smart interface which performs many of the functions normally found in a small terminal. The DISPLAY PROCESSOR CONTROLLER is designed around a slave microprocessor or custom LSI integrated circuit that provides display storage and multiplexing with a very minimum of circuit complexity. The simplest DISPLAY PROCESSOR CONTROLLER designed for a 16 digit 18 segment alphanumeric display is shown in Figure

17. This circuit is designed around the Intel 8279 Programmable Keyboard/Display Interface. This LSI chip contains the circuitry necessary to interface directly to a microprocessor bus and provides a 16 x 8 RAM, programmable scan counter, and keyboard debounce and control logic. While the 8279 is specifically designed for 7 segment displays, inclusion of the Texas Instruments AC5947 ASCII to 18 segment decoder/driver allows the use of an 18 segment alphanumeric display. The 8279 Keyboard/Display Controller interfaces to a microprocessor via an eight line bidirectional Data Bus, control lines RD (Read), WR (Write), CS (Chip Select), Ao (Command/Data), RESET, IRQ (Interrupt Request), and a clock input, CLK. The display is scanned by outputs A<sub>0-3</sub> and  $B_{0-3}$  which are connected to the inputs of the AC5947, and outputs SL0-3 which are connected to the digit scanning circuitry. The 74LS122 is used to provide interdigit blanking to prevent display ghosting. In addition to display scanning, the 8279 also has the ability to scan many different types of encoded or decoded keyboards, X-Y matrix keyboards, or provide a strobed data input to the microprocessor. The 8279 provides for either block data entry, where data enters from left to right across the display overflowing to the leftmost display location; right data entry, where data enters at the righthand side of the display and previous data shifts toward the left; and RAM data entry, where a four bit field in the control word specifies the address at which the next data word will be written. The 8279 allows data written into the display to be read by the microprocessor, and provides commands to either blank or clear the display.

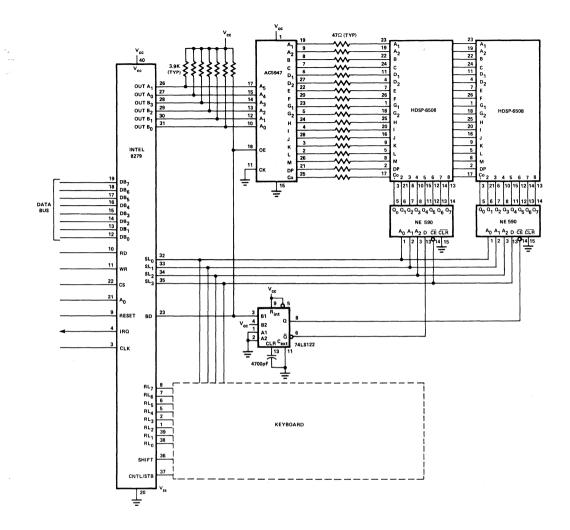

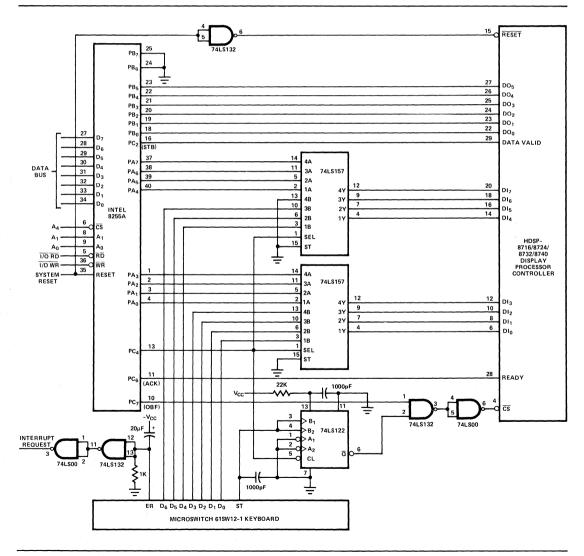

The HDSP-8716/-8724/-8732/-8740 DISPLAY PROCES-SOR CONTROLLER shown in Figure 18 is designed to provide a flexible 18 segment display interface for displays up to 40 characters in length. This circuit utilizes a dedicated Intel 8048 single chip microprocessor to provide features such as a blinking cursor, display editing routines, multiple data entry modes, variable display string length, and data out. This controller is available as a series of printed circuit board subsystems of 16, 24, 32, and 40 characters in length. The user interfaces to the 8048 microprocessor through eight Data In inputs, six Address inputs, a Chip Select input, Reset input, Blank input, six Data Out outputs, Data Valid output, Refresh output, and Clock output. The software within the 8048 microprocessor provides four data entry modes - Left Entry with a blinking cursor, Right Entry, Block Entry, and RAM Entry. The Data Out port allows the user to read the ASCII data stored within the display, determine the configured data entry mode and display length, and locate the position of the cursor within the display. Since the Data Out port is separate from the Data In port, the 18 segment DISPLAY PROCESSOR CONTROLLER can be used for text editing independent of the main microprocessor system. In Left Entry mode, the controller provides the Clear, Carriage Return, Backspace, Forwardspace, Insert, and Delete editing functions; while in Right Entry mode, the controller provides Clear and Backspace editing functions. The controller can also be expanded into multiple line panels.

The 8048 microprocessor interfaces to the display via the Port 2 output. The output is configured to enable the microprocessor to send a six bit word to <u>one of</u> three destinations as selected by  $P_{26}$  and  $P_{27}$ . The PROG output

### Figure 17. HDSP-6508 DISPLAY PROCESSOR CONTROLLER Utilizing the Intel 8279 Programmable Keyboard Display Interface

is then used to store this word at the specified destination. Destinationo is the 74LS174 hex register. The outputs of this register are decoded by the 74LS259 addressable latches and Sprague ULN 2815 digit drivers. Output 3F16 is decoded to turn on the rightmost display digit while the address of the leftmost display digit varies from 1816 for a 40 character display to 3016 for a 16 character display. Destination1 is the AC5947 18 segment decoder/driver. The positive edge of PROG stores a six bit ASCII code within the AC5947. Because destination1 is pulsed once every time a digit is refreshed, this output is also used as the Refresh output. Destination2 is the Data Valid output of the Data Out port. Thus, Data Out actually consists of a series of six bit words that are sent to Destination<sub>2</sub>. Display refresh is accomplished by first turning off the digit drivers by outputting a 016 to the 74LS174. Then a new ASCII character is stored within the AC5947. Finally, a new digit

word is stored within the 74LS174. The actual time that each digit is on varies according to the configured display length so as to provide a fixed 100 Hz refresh rate.

Interfacing the DISPLAY PROCESSOR CONTROLLER shown in Figure 18 to microprocessor systems depends on the needs of the particular application. Since the information on the Data In and Address inputs is loaded into the controller through a program within the 8048 microprocessor, the time required to read these inputs varies from about 100 to 700 microseconds. A latch as shown in the HDSP-8716/-8724/-8732/-8740 Data Sheet can be used as a buffer between these inputs and the data bus and address bus of the main microprocessor system. The latch provides temporary storage to avoid making the main microprocessor wait for the DISPLAY PROCESSOR CONTROLLER to accept data.

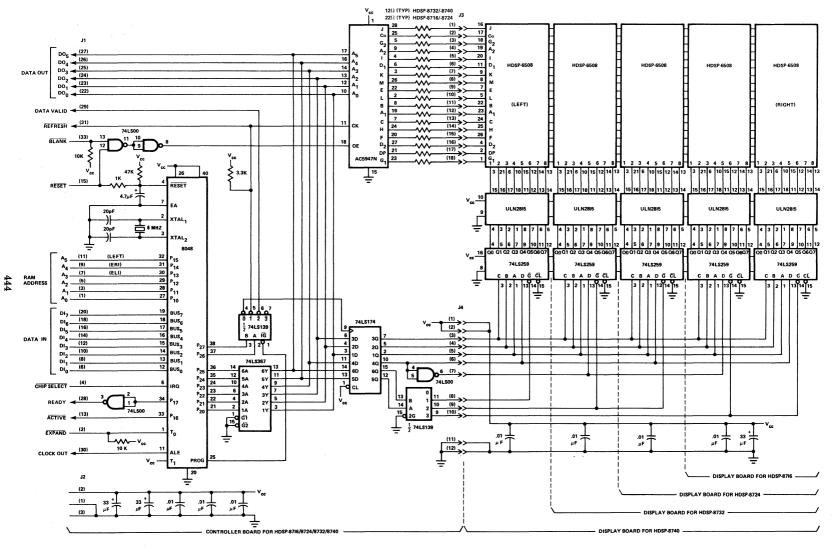

The 18 segment DISPLAY PROCESSOR CONTROLLER shown in Figure 18 can also be interfaced to the main microprocessor system through a Peripheral Interface Adapter (PIA). The Data In inputs of the controller would be connected to an output port of the PIA. In RAM Entry mode, the Address inputs of the controller would be connected to another output port of the PIA. The PIA provides a handshake back to the main microprocessor system that tells when the DISPLAY PROCESSOR CONTROLLER is ready to accept another data input word from the main microprocessor. This allows the microprocessor to load data into the controller at the highest possible rate. A PIA can also be used to allow the 18 segment DISPLAY PROCESSOR CONTROLLER to act as a buffer between a keyboard and the main microprocessor. In this configuration, the main processor could output a prompting message to the user via the DISPLAY PROCESSOR CONTROLLER. The user could then enter data from the keyboard into the display utilizing the controller's editing capability. After the message has been entered and edited, the user would instruct the main microprocessor to read the final edited message from the Data Out port. One port from the PIA can be used to control the Data In inputs of the DISPLAY PROCESSOR CONTROLLER and another port of the PIA can be used to read the Data Out port. Figure 19 shows a 6800 microprocessor system using a Motorola 6821 PIA to control the DISPLAY PROCESSOR CONTROLLER shown in Figure 18. The PB7 output of the PIA determines whether data is entered into the controller

Figure 19. 6800 Microprocessor Interface to the DISPLAY PROCESSOR CONTROLLER Shown in Figure 18 Utilizing a Motorola 6821 PIA

445

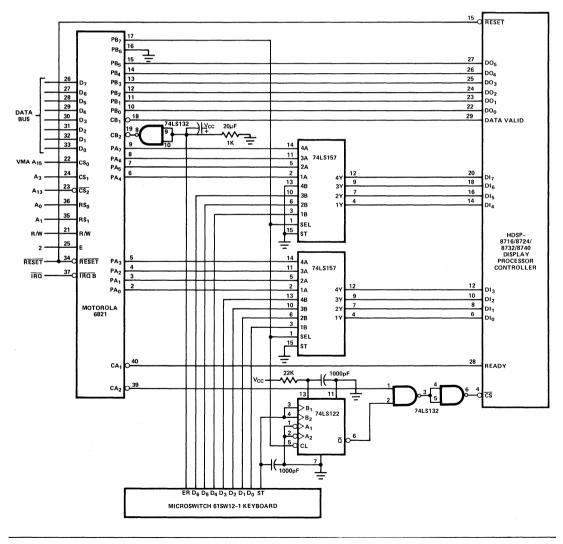

Figure 20. 6800 Microprocessor Program and Flowchart that Interfaces to the Circuit Shown in Figure 19

from the microprocessor system or from the keyboard. Control lines  $CA_1$  and  $CA_2$  are used to provide a data entry handshake to allow data to be loaded into the controller at the highest possible rate. Data is read into the main microprocessor system through Port B of the PIA using the CB<sub>1</sub> input as a data strobe.

The 6800 microprocessor program shown in Figure 20 is used to operate the PIA interface described in Figure 19. The microprocessor program following "START" is used to initialize the 6821 PIA. Once initialized, the PIA can be used either to load data into the controller via the main microprocessor, allow data to be loaded into the controller via the keyboard, or to read data from the Data Out port into the main microprocessor. The instruction CLR E, PRB at location 051B<sub>16</sub> forces PB<sub>7</sub> low to connect the outputs of Port A to the Data In inputs of the controller.

Subroutine "LOAD" then loads a series of eight bit words into the controller. "LOAD" continues to output words until it reads an FF<sub>16</sub> to denote the end of the prompting message. The instruction sequence LDA A I, \$80 and STA A E, PRB at location 052616 forces PB7 high to connect the output of the keyboard to the Data In inputs of the controller. In this mode, the user can enter or edit data into the DISPLAY PROCESSOR CONTROLLER. The 4B input of the 74LS157 has been grounded to prevent the keyboard from loading a control word into the DISPLAY PROCESSOR CONTROLLER. The instructions LDA A I, \$0E and STA A E. CRB at location 052B16 enables the "ER" key on the keyboard to interrupt the microprocessor when the edited message is complete. Subroutine "READ" would then be used to read data into the 6800 system. First, subroutine "READ" outputs a special control word,

Figure 22. 8080A Microprocessor Program and Flowchart that Interfaces to the Circuit Shown in Figure 21

FF16, to the Data In inputs of the DISPLAY PROCESSOR CONTROLLER. This control word causes the controller to begin its data output sequence. The controller outputs a series of data output words that define the configured entry mode and display length, location of the cursor, and the ASCII text stored within the DISPLAY PROCESSOR CONTROLLER. "LOOP 1" within the program continuously reads the Data Valid output and waits until the controller outputs the STATUS word. This STATUS word, the subsequent CURSOR ADDRESS word, and the string of ASCII characters are then stored in consecutive words of scratch pad memory starting at address "STATUS."

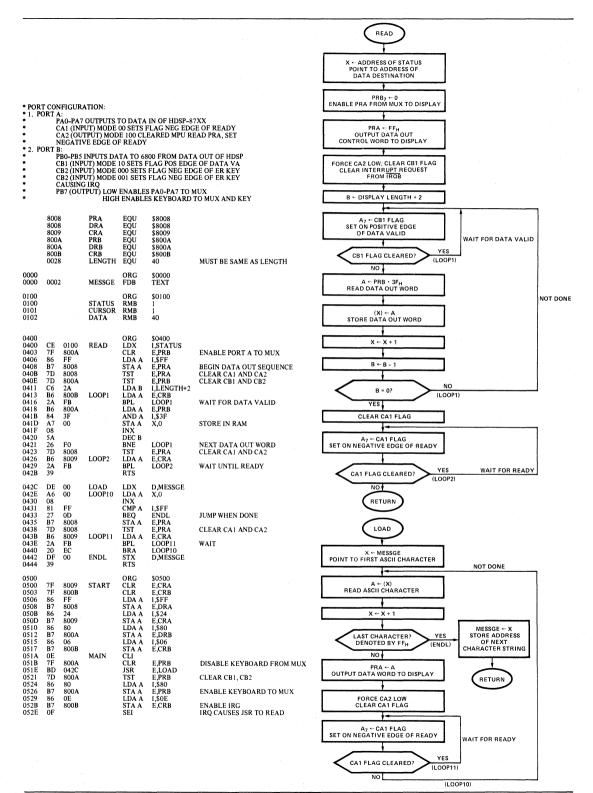

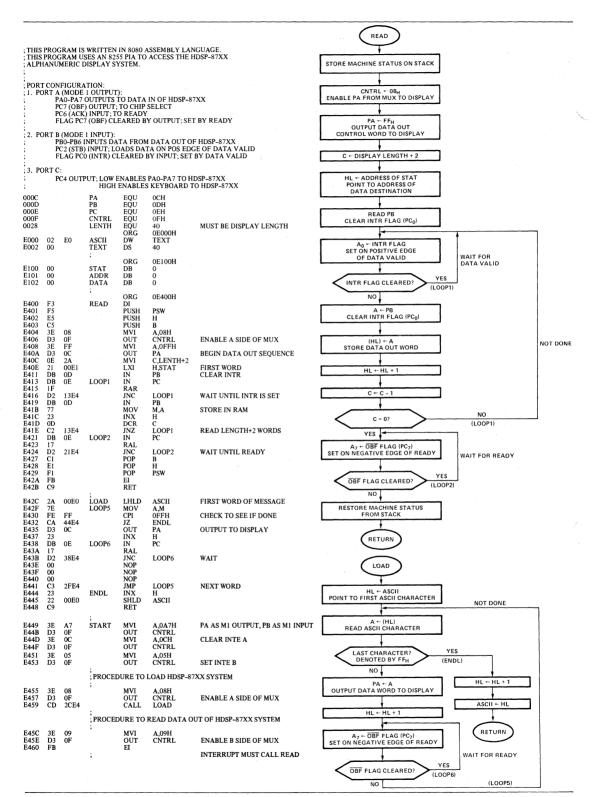

A similar PIA interface designed for an 8080A microprocessor system that uses an Intel 8255A PIA is shown in Figure 21. This interface operates in much the same way as the 6821 PIA interface that was previously described. The PC4 output of the PIA determines whether the Data In inputs of the 18 segment DISPLAY PROCESSOR CONTROLLER shown in Figure 18 are connected to the PIA or to the keyboard. Control lines PC<sub>6</sub> and PC<sub>7</sub> are used to provide a data entry handshake between the 8080A microprocessor and the DISPLAY PROCESSOR CONTROLLER. Data is read into the 8080A microprocessor system through Port B of the PIA using PC<sub>2</sub> as the data strobe. The 8080A microprocessor program shown in Figure 22 is used to operate the PIA interface described in Figure 21. The microprocessor program following "START" is used to initialize the 8255A PIA. The instructions MVI A. 08H and OUT CNTRL at location E45716 force PC4 low to connect Port A of the PIA to the Data In inputs of the DISPLAY PROCESSOR CONTROLLER. Subroutine "LOAD" would then be used to load a prompting message into the controller. The instructions MVI A. 09H and OUT CNTRL at location E45E16 connect the keyboard to the Data In inputs of the controller. In this mode, the user can enter data into the DISPLAY PROCESSOR CON-TROLLER, or to edit an existing line. Subroutine "READ" would then be used to read the data from the Data Out port into the 8080A microprocessor system.

Subroutine "READ" begins the data output sequence by outputting the special control word  $FF_H$  to the Data In inputs of the DISPLAY PROCESSOR CONTROLLER. Then, the subroutine reads the series of data output words that are outputted by the controller and stores them in consecutive words of scratch pad memory starting at address STAT.