**APPLICATION NOTE 1026**

# Designing with Hewlett-Packard's HPDL-2416 Smart Display

# TABLE OF CONTENTS

b

| INTRODUCTION                                                                                                                                                    | 1                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| ELECTRICAL DESCRIPTION                                                                                                                                          | 2                     |

| ELECTRICAL DESIGN CONSIDERATIONS   Writing and Displaying ASCII Data   Writing and Displaying Cursor Data   Clear Function   Blanking Function   Design Example | 4<br>4<br>6<br>7<br>7 |

| USING THE HPDL-2416 WITH<br>MICROPROCESSORS                                                                                                                     | 9                     |

| MEMORY MAPPED SYSTEM<br>Interfacing to the 8085 and Z-80 Microprocessors<br>Interfacing to the 6800<br>Using the Cursor, Blanking and Clear Function            | 9<br>12<br>12<br>14   |

| I/O MAPPED SYSTEM<br>Latch Technique<br>Handshaking Technique                                                                                                   | 14<br>14<br>16        |

| PREPROGRAMMED MESSAGE                                                                                                                                           | 18                    |

| MECHANICAL AND ELECTRICAL HANDLING<br>Soldering and Post Solder Cleaning<br>Socketing Considerations<br>Handling Considerations                                 | 21<br>22<br>22<br>22  |

| CONTRAST ENHANCEMENT                                                                                                                                            | 22                    |

|                                                                                                                                                                 |                       |

HEWLETT

PACKARD

#### INTRODUCTION

Hewlett-Packard's smart alphanumeric display, the HPDL-2416, is designed to minimize user design worries. Each HPDL-2416 displays four alphanumeric characters utilizing an on-board CMOS IC. The display is able to handle character storage, character decoding, multiplexing, segment driving and refreshing. Designers should treat the HDPL-2416 as a four-byte RAM, whose purpose is to store and display 64 character ASCII data using a sixteensegment character font as shown in Figure 1.

This note is intended to serve as a design and application guide for users of the HPDL-2416. The information presented will cover: electrical description, electrical design considerations, interfacing to microprocessors, preprogrammed message systems, mechanical and electrical handling, and contrast enhancement.

| BITS                                         | D <sub>3</sub><br>D <sub>2</sub><br>D <sub>1</sub><br>D <sub>0</sub> | 0<br>0<br>0 | 0<br>0<br>0<br>1 | 0<br>0<br>1<br>0 | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>0 | 0<br>1<br>0<br>1 | 0<br>1<br>1<br>0 | 0<br>1<br>1<br>1 | 1<br>0<br>0<br>0 | 1<br>0<br>0<br>1 | 1<br>0<br>1<br>0 | 1<br>0<br>1<br>1 | 1<br>1<br>0<br>0 | 1<br>1<br>0<br>1 | 1<br>1<br>1<br>0 | 1<br>1<br>1 |

|----------------------------------------------|----------------------------------------------------------------------|-------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|-------------|

| D <sub>6</sub> D <sub>5</sub> D <sub>4</sub> | HEX                                                                  | 0           | 1                | 2                | 3                | 4                | 5                | 6                | 7                | 8                | 9                | A                | В                | С                | D                | E                | F           |

| 0 1 0                                        | 2                                                                    | (space)     | !                | П                | #                | 5                | 炻                | Z                | 1                | <                | >                | Ж                | +                | 1                | —                |                  | 1           |

| 0 1.1                                        | 3                                                                    |             |                  | 2                | 3                | 4                | 5                | 6                | 7                | Β                | 9                | -                |                  | 2                | _                | 7                | 7           |

| 1 0 0                                        | 4                                                                    | 司           | A                | B                |                  | IJ               | E                | F                | G                | Н                | I                | J                | К                | L                | M                | N                |             |

| 101                                          | 5                                                                    | $\square$   |                  | R                | 5                | Т                |                  | V                | W                | X                | Y                | Ζ                | E                | 1                | ]                | ~                |             |

Figure 1. HPDL-2416 ASCII Character Set

ADVANCED SEMICONDUCTOR DEVICES (PTY) LTD. P.O. BOX 2944 JOHANNESBURG 2000 TEL. 802-5820

# **ELECTRICAL DESCRIPTION**

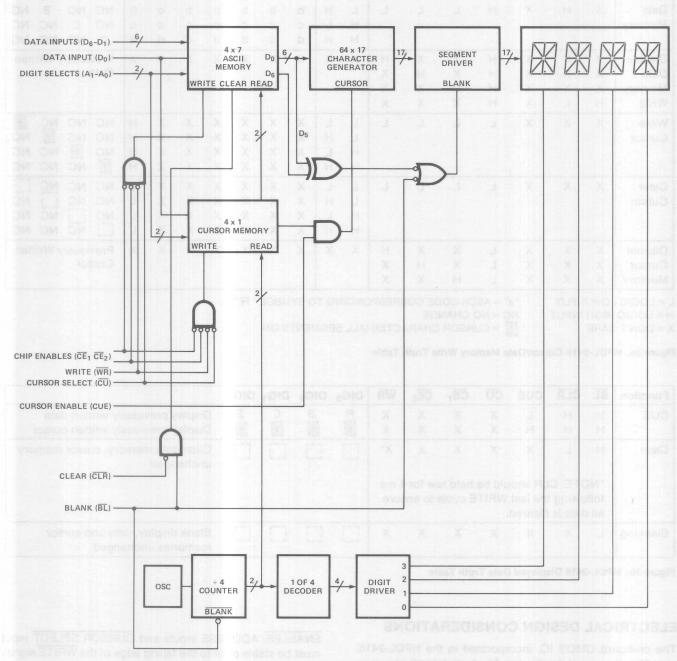

Figure 2 shows the internal block diagram of the HPDL-2416. It consists of two parts: the display LEDs and the CMOS IC. The CMOS IC is designed to operate from  $-20^{\circ}$ C to  $+70^{\circ}$ C; over this temperature range the inputs operate on standard TTL voltages (V<sub>IH</sub> = 2.0 V min., V<sub>IL</sub> = 0.8 V max.). The IC can store a maximum of four characters in ASCII memory and four cursors in CURSOR memory. Every location in ASCII memory stores one 7 bit ASCII character; each CURSOR memory location contains a single bit that denotes the presence or absence of a cursor. (All segments will be ON when a cursor is displayed.) Each location in memory may be randomly accessed. After a character has been written to memory the IC decodes the ASCII data, drives the display and refreshes it without any external hardware or software.

The HPDL-2416 uses 18 pins to control the CMOS IC. Figure 2 shows the effect these inputs have on the display. The following list summarizes the various display pin functions and their associated abbreviations. Please note for reasons of simplicity, text rather than abbreviations will be used to denote pin functions in this application note.

CHIP ENABLE INPUTS (CE1 and CE2, pins 1 and 2) These inputs must be at a logic low to write to the display. They can be used to cascade multiple display systems with minimal additional hardware.

CLEAR (CLR pin 3)

ASCII data will be removed from the ASCII memory after the CELAR input has been held at a logic low for ms. CURSOR data is unaffected by the CLEAR input.

CURSOR ENABLE INPUT (CUE pin 4)

The IC uses CUE to determine whether it displays the ASCII memory or the CURSOR memory. (1 = CURSOR, 0 = ASCII). CURSOR SELECT INPUT (CU pin 5)

WRITE (WR pin 6)

ADDRESS INPUTS (A1 and A0, pins 8 and 7)

Vcc and GND (pins 9 and 10) DATA INPUTS (D<sub>0</sub>-D<sub>6</sub>, pins 11-17)

#### BLANKING (BL pin 18)

This input is used by the IC to determine whether data is stored in ASCII memory or CURSOR memory. (1 = ASCII, 0 = CURSOR).

Data is written into the display when the WR input is low and the display has been selected.

Each location in memory has a distinct address. ADDRESS inputs enable the designer to select a specific location in memory to store data. Address 00 accesses the far right display location. Address 11 accesses the far left location.

These pins supply power to the display

Seven bit ASCII data is entered into the ASCII memory via the DATA inputs. CURSOR data is stored in the CURSOR memory when the CU input is a logic low. Do determines if a CURSOR is stored or removed from CURSOR memory. (1 = store cursor, 0 = remove cursor)

The BLANKING input can be used to create a flashing display or to blank the display without clearing the ASCII memory. This input inhibits the IC segment drivers and the display CLEAR (CLR) pin.

The on-board CAROS IC, incorporate in the InfoCratics simplifies the use of the disulary. The truth table is shown in Figure 3, Figure 14 shows how to write data to the ASO and CURSOR minimates Figure 3b shows the ppendice of me CURSOR minimates Figure 3b shows the ppendice of

aderion to the truth table, correct timing is necessary for reliable operation of the part. Finking for the PPOL-2416 is in Figure 4. Individual excitables show the context topic layele to ford and display data load and use the curson and clear and blunk the display. These examples are illustrated in Figures 5.0.7.0 and 8;

Adding and Digulaying ASCH Data

Figure 5 shows the appropriate logic levels to write and display ASCI should be ASCII data is entered via the DATA imputs 30 D1 and is sterve in the memory location indicated by the ASDR1555 Inputs An-Ar. The CURSUR SELECT should be togic 1 to write ASCII data to the display As shown with the limits display an of Figure 4, the OHP

Agnal AGOII data Auli ogi c levels ano ogi c levels ano ogenerate To and 64 charac nout Os la Ine DATA Inputs Cr hata will be no be decoded by hata sut 54 ch wort to use the

Figure 2. HPDL-2614 Internal Block Diagram

in Figure 5b are maintained. It is possible different input codes with assen DATA is the ASCH character set in Figure 1, di ASCH codes are crimited when DATA of Da are in the stime logical clate, meal of Da are in the stime logical clate, invelition the display memory. Unreste clate with art Ca is a blabk character and Diagness who solve ASCH character and Diagness who

| Function | BL | CLR | CUE | CU | $\overline{CE}_1$ | $\overline{CE}_2$ | WR | A <sub>1</sub> | A <sub>0</sub> | D <sub>6</sub> | <b>D</b> <sub>5</sub> | D <sub>4</sub> | <b>D</b> <sub>3</sub> | D <sub>2</sub> | <b>D</b> <sub>1</sub> | $D_0$ | DIG3DIG2DIG1DIG0   |

|----------|----|-----|-----|----|-------------------|-------------------|----|----------------|----------------|----------------|-----------------------|----------------|-----------------------|----------------|-----------------------|-------|--------------------|

| Write    | L  | Х   | Х   | Н  | L                 | L                 | L  | L              | L              | а              | а                     | а              | а                     | а              | а                     | а     | NC NC NC A         |

| Data     | Х  | Н   | Х   | н  | L                 | L                 | L  | L              | Н              | b              | b                     | b              | b                     | b              | b                     | b     | NC NC B NC         |

| Memory   |    |     |     |    |                   |                   |    | н              | L              | С              | С                     | С              | С                     | С              | С                     | С     | NC E NC NC         |

| 1000     |    |     |     |    |                   |                   |    | н              | Н              | d              | d                     | d              | d                     | d              | d                     | d     | D NC NC NC         |

| Disable  | Х  | Х   | Х   | Н  | Х                 | Х                 | Н  | X              | Х              | Х              | Х                     | Х              | Х                     | Х              | Х                     | Х     | Previously Written |

| Data     | Х  | X   | Х   | н  | Х                 | н                 | Х  | MBR.           |                |                |                       |                |                       |                |                       |       | Data               |

| Memory   | Х  | X   | Х   | н  | н                 | Х                 | X  | Brings         |                | 1.1            |                       |                |                       |                |                       |       |                    |

| Write    | н  | L   | Х   | Н  | Х                 | Х                 | Х  |                |                |                |                       |                |                       |                |                       |       |                    |

| Write    | Х  | Х   | Х   | L  | L                 | L                 | L  | L              | L              | Х              | Х                     | Х              | Х                     | Х              | Х                     | Н     | NC NC NC           |

| Cursor   |    |     |     |    |                   |                   |    | L              | н              | X              | Х                     | Х              | Х                     | Х              | Х                     | н     | NC NC NC           |

|          |    |     |     |    |                   |                   |    | н              | L              | X              | Х                     | Х              | Х                     | Х              | Х                     | н     | NC X NC NC         |

|          |    |     |     |    |                   |                   |    | н              | Н              | X              | Х                     | Х              | Х                     | Х              | Х                     | Н     | NC NC NC           |

| Clear    | Х  | Х   | Х   | L  | L                 | L                 | L  | L              | L              | X              | Х                     | Х              | Х                     | Х              | Х                     | L     | NC NC NC           |

| Cursor   |    |     |     |    |                   |                   |    | L              | н              | X              | Х                     | Х              | Х                     | X              | Х                     | L     | NC NC NC           |

|          |    |     |     |    |                   |                   |    | н              | L              | X              | X                     | Х              | Х                     | Х              | Х                     | L     | NC TINC NC         |

|          |    |     |     |    |                   |                   |    | н              | Н              | X              | Х                     | Х              | Х                     | Х              | Х                     | L     | [] NO NO NO        |

| Disable  | Х  | Х   | Х   | L  | Х                 | Х                 | н  | X              | Х              | X              | Х                     | Х              | Х                     | X              | Х                     | Х     | Previously Written |

| Cursor   | X  | Х   | Х   | L  | Х                 | н                 | Х  |                |                |                |                       |                |                       |                |                       |       | Cursor             |

| Memory   | X  | Х   | Х   | L  | н                 | Х                 | Х  |                |                |                |                       |                |                       |                |                       |       |                    |

L = LOGIC LOW INPUT H = LOGIC HIGH INPUT "a" = ASCII CODE CORRESPONDING TO SYMBOL " $\Pi$ " NC = NO CHANGE

A = LOGIC HIGH INPLX = DON'T CARE

= CURSOR CHARACTER (ALL SEGMENTS ON)

Figure 3a. HPDL-2416 Cursor/Data Memory Write Truth Table

| Function | BL     | CLR    | CUE                                | CU     | CE <sub>1</sub> | $\overline{CE}_2$ | WR     | DIG <sub>3</sub> | DIG <sub>2</sub> | DIG <sub>1</sub> | DIG <sub>0</sub> |                                                                      |

|----------|--------|--------|------------------------------------|--------|-----------------|-------------------|--------|------------------|------------------|------------------|------------------|----------------------------------------------------------------------|

| CUE      | H<br>H | H<br>H | L<br>H                             | X<br>X | X<br>X          | ×<br>×            | X<br>X | F<br>K           | E                | с<br>Ж           |                  | Display previously written data<br>Display previously written cursor |

| Clear    | foll   | owing  | X<br>LR sho<br>the last<br>cleared | WRIT   |                 |                   |        | []]              | []]              | []]              | []]              | Clear data memory, cursor memory<br>unchanged                        |

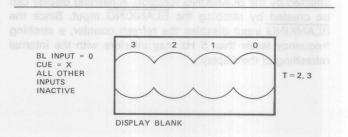

| Blanking | L      | Х      | Х                                  | Х      | Х               | Х                 | Х      | []]              | []]              | []]              | [_]              | Blank display, data and cursor memories unchanged.                   |

Figure 3b. HPDL-2416 Displayed Data Truth Table

# **ELECTRICAL DESIGN CONSIDERATIONS**

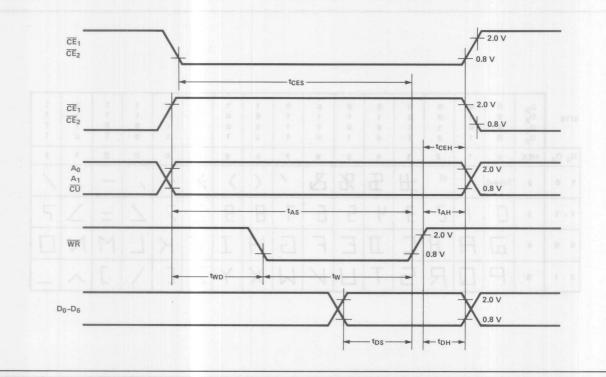

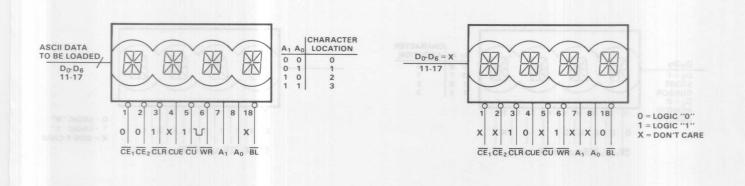

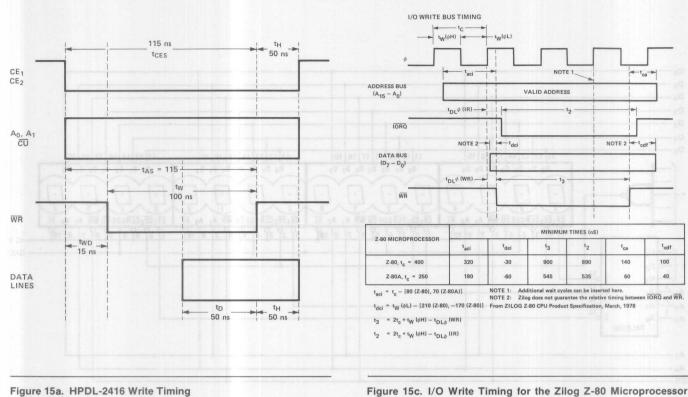

The on-board CMOS IC, incorporated in the HPDL-2416, simplifies the use of the display. The truth table is shown in Figure 3. Figure 3a shows how to write data to the ASCII and CURSOR memories. Figure 3b shows the operation of the CURSOR SELECT, BLANKING, AND CLEAR inputs. In addition to the truth table, correct timing is necessary for reliable operation of the part. Timing for the HPDL-2416 is in Figure 4. Individual examples show the correct logic levels to load and display data, load and use the cursor, and clear and blank the display. These examples are illustrated in Figures 5, 6, 7, 8 and 9.

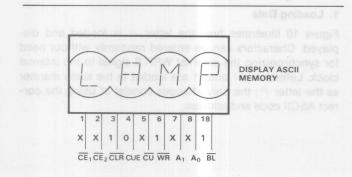

# Writing and Displaying ASCII Data

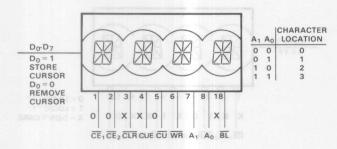

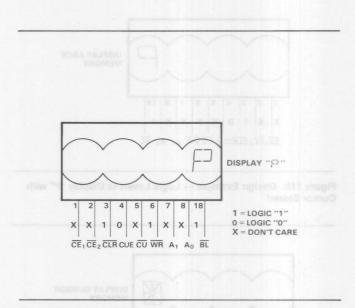

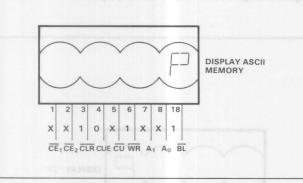

Figure 5 shows the appropriate logic levels to write and display ASCII characters. ASCII data is entered via the DATA inputs D<sub>0</sub>-D<sub>6</sub> and is stored in the memory location indicated by the ADDRESS inputs A<sub>0</sub>-A<sub>1</sub>. The CURSOR SELECT should be logic 1 to write ASCII data to the display. As shown in the timing diagram of Figure 4, the CHIP ENABLES, ADDRESS inputs and CURSOR SELECT input must be stable prior to the falling edge of the WRITE signal. The DATA inputs need to be stable prior to the rising edge of the WRITE signal. The DATA, ADDRESS, CHIP SELECT and CURSOR SELECT inputs must be held stable until a specified hold time following the rising edge of the WRITE signal.

ASCII data will be decoded and displayed as long as the logic levels shown in Figure 5b are maintained. It is possible to generate 128 different input codes with seven DATA inputs. Referring to the ASCII character set in Figure 1, all valid 64 character ASCII codes are created when DATA input D<sub>5</sub> is the logical complement of DATA input D<sub>6</sub>. If DATA inputs D<sub>5</sub> and D<sub>6</sub> are in the same logical state, invalid data will be stored in the display memory. (Invalid data will be decoded by the IC as a blank character). Figure 6 shows the 6 bit 64 character ASCII character set. Designers who wish to use the 6 bit 64 character ASCII set can invert D<sub>5</sub> to generate D<sub>6</sub>.

| Parameter              | Symbol       | –20° C<br>t <sub>MIN</sub> | 25°C<br>t <sub>MIN</sub> | 70° C<br>t <sub>MIN</sub> | Units |

|------------------------|--------------|----------------------------|--------------------------|---------------------------|-------|

| Address Setup Time     | tas          | 90                         | 115                      | 150                       | ns    |

| Write Delay Time       | twp          | 10                         | 15                       | 20                        | ns    |

| Write Time             | tw           | 80                         | 100                      | 130                       | ns    |

| Data Setup Time        | tDS          | 40                         | 60                       | 80                        | ns    |

| Data Hold Time         | tDH          | 40                         | 45                       | 50                        | ns    |

| Address Hold Time      | tan          | 40                         | 45                       | 50                        | ns    |

| Chip Enable Hold Time  | tсен         | 40                         | 45                       | 50                        | ns    |

| Chip Enable Setup Time | tCES         | 90                         | 115                      | 150                       | ns    |

| Clear Time             | tCLR         | 2.4                        | 3.5                      | 4.0                       | ms    |

| Access Time            | IN CLEANTING | 130                        | 160                      | 200                       | ns    |

| Refresh Rate           |              | 420-790                    | 310-630                  | 270-550                   | Hz    |

Figure 5a. Logic Levels to Load ASCII Memory

Figure 5b. Logic Levels to Display ASCII Memory

5

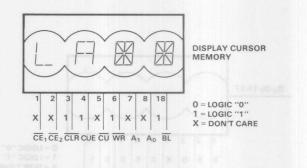

#### Writing and Displaying Cursor Data

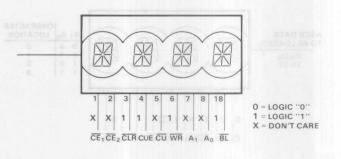

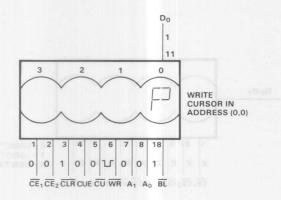

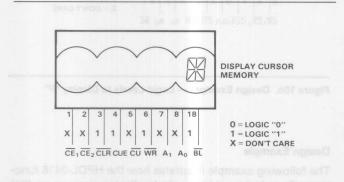

Figure 7 illustrates the proper logic levels to write and display CURSOR data. The CURSOR SELECT should be logic 0 to write a cursor to the display. DATA input, D<sub>0</sub>, is used by the IC to enter or remove a cursor from CURSOR memory. If D<sub>0</sub> = 1, a cursor will be entered; if D<sub>0</sub> = 0, a cursor will be removed. The ADDRESS inputs select the location in memory to store CURSOR data. Writing CURSOR data requires the same timing as writing ASCII data. As shown in the timing diagram of Figure 4 the CHIP ENABLES, ADDRESS inputs and CURSOR SELECT input should be stable prior to the falling edge of the WRITE signal; DATA input, D<sub>0</sub>, needs to be stable prior to the rising edge. D<sub>0</sub>, ADDRESS, CHIP ENABLE and CURSOR SELECT inputs must be held stable until a specified hold time following the rising edge of the WRITE signal. CURSOR data will be decoded and displayed as long as the logic levels shown in Figure 1b are maintained. If a location in CURSOR memory does not have a CURSOR stored in it, the CMOS IC will display the contents of the ASCII memory for that location. A flashing cursor can be generated by strobing the CURSOR ENABLE input.

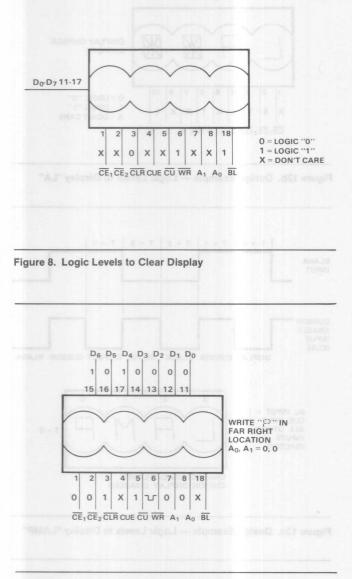

#### **Clear Function**

Figure 8 shows the logic levels necessary to clear the display. The CLEAR input fills the ASCII memory with blanks without affecting the contents of the CURSOR memory. Clearing is accomplished by sequentially writing a blank character to each location in ASCII memory using the internal refresh clock. At worst case, the CMOS IC requires

ms to clear the display. If the BLANKING input is logic 0, the CLEAR function will be inhibited.

| BITS                          | D <sub>3</sub><br>D <sub>2</sub><br>D <sub>1</sub><br>D <sub>0</sub> | 0<br>0<br>0 | 0<br>0<br>0<br>1 | 0<br>0<br>1<br>0 | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>0 | 0<br>1<br>0<br>1 | 0<br>1<br>1<br>0 | 0<br>1<br>1<br>1 | 1<br>0<br>0<br>0 | 1<br>0<br>0<br>1 | 1<br>0<br>1<br>0 | 1<br>0<br>1<br>1 | 1<br>1<br>0<br>0 | 1<br>1<br>0<br>1 | 1<br>1<br>1<br>0 | 1<br>1<br>1<br>1 |

|-------------------------------|----------------------------------------------------------------------|-------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| D <sub>5</sub> D <sub>4</sub> | HEX                                                                  | 0           | 1                | 2                | 3                | 4                | 5                | 6                | 7                | 8                | 9                | A                | в                | С                | D                | E                | F                |

| 1 0                           | 2                                                                    | (space)     | )!               | 11               | Щ                | 5                | 炻                | Z                | 1                | <                | $\rangle$        | Ж                | H                | 1                |                  | 14<br>14<br>15   | /                |

| 1 . 1                         | 3                                                                    |             | 1                | 2                | Ξ                | 4                | 5                | 6                | 2                | Β                | 9                | -                |                  | L                | =                | 7                | 7                |

| 0 0                           | 4                                                                    | 司           | A                | B                |                  |                  | E                | F                | G                | H                | I                | J                | К                | L                | Μ                | N                |                  |

| 0 1                           | 5                                                                    | 日           |                  | R                | 5                | Т                |                  | V                | W                | X                | Y                | Ζ                | E                | 1                | ]                | ~                |                  |

Figure 7a. Logic Levels to Load Cursor Memory

Figure 7b. Logic Levels to Display Cursor Memory

Figure 6. HPDL-2416 6-bit ASCII Character Set

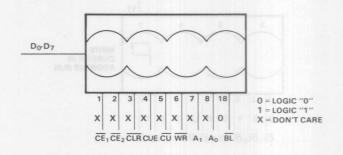

Figure 10a. Design Example - Logic Levels to Write "P"

Figure 9. Logic Levels to Blank the Display

Figure 10b. Design Example — Logic Levels to Display "P"

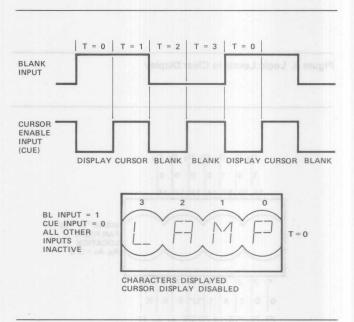

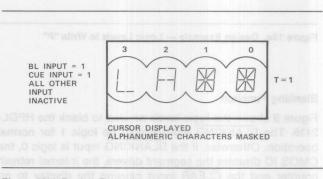

#### **Blanking Function**

Figure 9 shows the logic levels needed to blank the HPDL-2416. The BLANKING input should be logic 1 for normal operation. Otherwise, if the BLANKING input is logic 0, the CMOS IC disables the segment drivers, the internal refresh counter and the CLEAR input causing the display to go blank. Neither ASCII memory nor CURSOR memory is affected by the BLANKING function. A flashing display can be created by strobing the BLANKING input. Since the BLANKING input disables the refresh counter, a strobing frequency faster than 5 Hz may interfere with the internal refreshing of the display.

#### **Design Example**

The following example illustrates how the HPDL-2416 functions. The design objective is to display a message that consists of the word  $\Box \sqcap \bowtie \sqcap$  plus a flashing cursor in the two far right locations.

#### 1. Loading Data

Figure 10 illustrates how the letter P is loaded and displayed. Characters can be entered randomly without need for synchronizing the external WRITE signal to the internal clock. Letters L, P and M are loaded in the same manner as the letter P; the only changes consist of using the correct ASCII code and address.

Figure 11a. Design Example — Logic Levels to Write Cursor in the "P" Location

Figure 11b. Design Example — Logic Levels to Display "P" with Cursor Stored

Figure 11c. Design Example - Logic Levels to Display Cursor

Figure 12b. Design Example — Logic Levels to Display "LA"

Figure 13a. Design Example — Logic Levels to Display "LAMP"

Figure 12a. Design Example — Logic Levels to Display "LAMP"

Figure 13c. Design Example — Logic Levels to Blank Display

#### 2. Loading Cursor

Figure 11 illustrates how a CURSOR is loaded into the display using the same address as the letter P. (It is important to note letter P is still being displayed). CURSORS may be written in or removed from any character location by using the DATA input, D<sub>0</sub>, and the corresponding addresses.

#### 3. Flashing Cursor and Blanking

As shown in Figure 12, strobing the CUE input causes the HPDL-2416 to alternate between displaying  $\bot \sqcap \bowtie \urcorner$  and displaying two cursors. Exceeding the strobing limit of 5 Hz may cause the eye to perceive only the cursor. If BLANKING = 0, the display will be blank. Strobing both CURSOR and BLANKING with the waveforms shown in Figure 13 will cause the HPDL-2416 ENABLE to display the following sequence:  $\bot \sqcap \bowtie \urcorner$ ,  $\bot \sqcap \boxtimes \boxtimes$ , BLANK, BLANK,  $\bot \sqcap \bowtie \urcorner$ ...

# USING THE HPDL-2416 WITH MICROPROCESSORS

Several different techniques can be used to interface an HPDL-2416 to a microprocessor. The HPDL-2416 is sufficiently versatile to be configured as either a memory device in a memory mapped system or as an output device in an I/O mapped system. Both types of systems will be covered. All microprocessor addresses in the following examples have been selected for illustrative purposes only. They can be changed to suit the designer's needs.

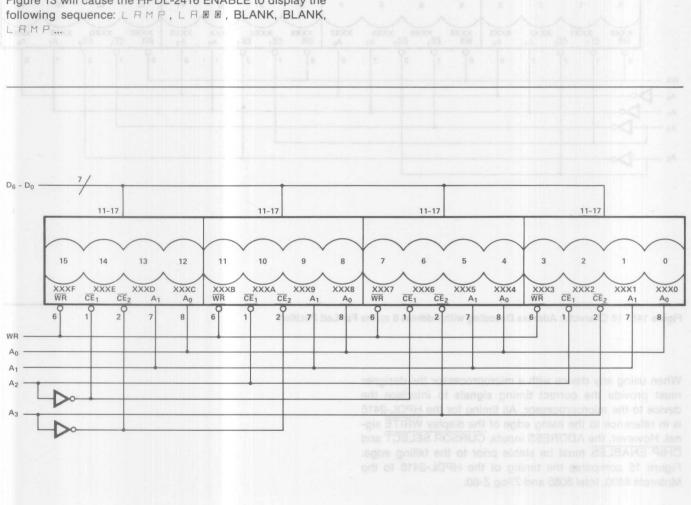

Figure 14a. 16 Character Address Decoding with Address 0 as the Far Right Position

# MEMORY MAPPED SYSTEM

The easiest method is to configure the HPDL-2416 as a memory device. Each character in the display will use one memory location. A 16 character length display requires the use of 16 memory locations. Address decoding is simplified by using the two CHIP ENABLEs. For a 16 character display, microprocessor address lines A<sub>0</sub> and A<sub>1</sub> would be connected directly to four HPDL-2416 displays. Using two

inverters to generate  $A_2$  and  $A_3$ , the appropriate combinations of  $A_2$ ,  $A_2$ ,  $A_3$  and  $A_3$  would be connected to the CHIP ENABLEs to select the appropriate display. Thus, the 16 character display would be located at microprocesor addresses XXX0 to XXXF. Figure 14 shows how a 16 character display system can be formatted to allow for the 16 addresses to be organized with either address 0 or address F being the far left display character.

NO DUIDEON N

Figure 11 divertities how a CURSOR is loaded into the discess using the same address as the latter P. III is important to note letter P. Is still being displayed. CURSORS may be written in or removed from any chatacter location by using the DATA input, On and the corresponding addresses.

- Flashing Curron and Slanking

a shown in Figure 12, strabing the CUE input causes the

# USING THE REDUCTION WITH

everal different todaniq les ci PDL-2416 to a micropy Joses ently versatile to be configures a memory mapped system c O mapped system. Soil types Il microprocessor addivesta type been selected for ill strati-

hold sea can be used to interfact apprusses to the HPDL-2416 is configured as either a memory of syriem or as an output davice Both types of systems will be cov addresses in the following exam-

Figure 14b. 16 Character Address Decoding with Address 0 as the Far Left Position

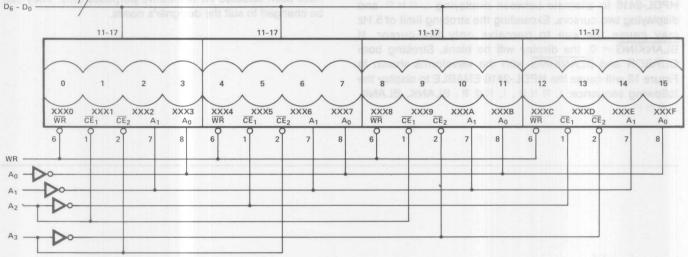

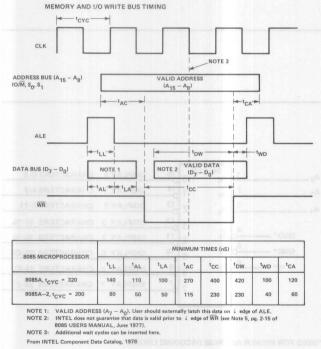

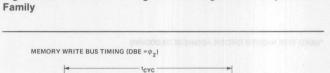

When using any device with a microprocessor the designer must provide the correct timing signals to interface the device to the microprocessor. All timing for the HPDL-2416 is in reference to the rising edge of the display WRITE signal. However, the ADDRESS inputs, CURSOR SELECT and CHIP ENABLES must be stable prior to the falling edge. Figure 15 compares the timing of the HPDL-2416 to the Motorola 6800, Intel 8085 and Zilog Z-80.

Flower 14m, 10 Charterier Address Deceding with Address 0 as the Far Right Position

#### MEMORY MAPPED SYSTEM

The easiest method is to configure the HPDL-2416 as a menory device. Each character in the display will use one memory location. A 16 character length display requires the use of 16 memory locations. Address decoding is simplified by using the two CHIP EtKABLET. For a 16 character display, microprocessor, address lines Ap and Ar, would be connected electly to four HPDL-2416 displays. Using two

and As, the appropriate combinawould be connected to the CHIP oppropriate display. Thus, the 16 d be located at microprocessor Figure 14 shows now a 16 characbe formatted to allow for the 18 d with either address 0 or appress character.

Figure 15a. HPDL-2416 Write Timing

Figure 15d. Memory Write Timing for the Motorola 6800 Microprocessor Family

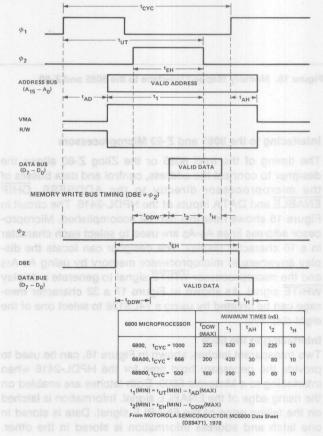

Figure 16. Memory Mapped Interface to the 8085 and Z-80

#### Interfacing to the 8085 and Z-80 Microprocessors

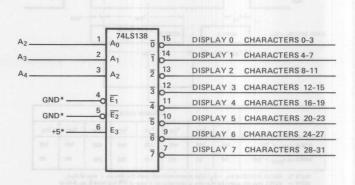

The timing of the Intel 8085 or the Zilog Z-80 allows the designer to connect the address, control and data busses of the microprocessor directly to the ADDRESS, CHIP ENABLE and DATA inputs of the HPDL-2416. The circuit in Figure 16 shows how this can be accomplished. Microprocesor address lines  $A_0$ - $A_3$  are used to select each character in a 16 character display. The designer can locate the display anywhere in microprocessor memory by using A4-A15 and the microprocessor WRITE signal to generate a dsiplay WRITE signal. As shown in Figure 17 a 32 character message can be created by using a 74LS138 to select one of the eight displays.

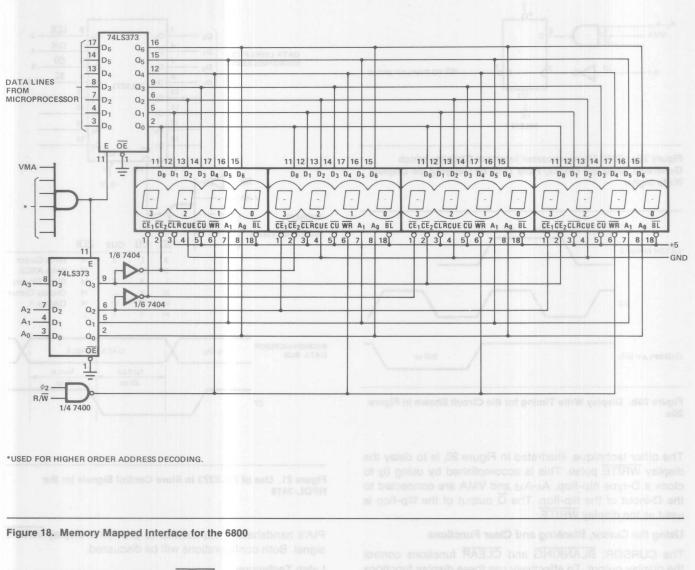

#### Interfacing to the 6800

Two transparent latches, shown in Figure 18, can be used to provide the necessary hold time for the HPDL-2416 when interfacing to a Motorola 6800. Both latches are enabled on the rising edge of the ENABLE signal. Information is latched on the falling edge of the ENABLE signal. Data is stored in one latch and address information is stored in the other. The address of the display in microprocessor memory is defined by a logical combination of A4-A15 and VMA which is used to generate an ENABLE signal for these latches.

\*USED FOR HIGHER ADDRESS DECODING ORDER.

Figure 17. 32 Character Address Decoder Technique for the HPDL-2416

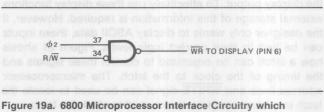

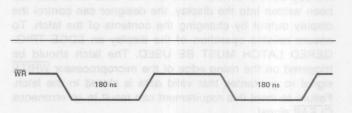

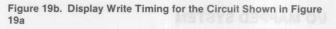

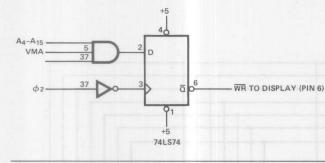

It is essential that the display WRITE signal generated by the interface circuitry allows the DATA inputs to stabilize prior to the rising edge. Figures 19 and 20 illustrate two circuits can be used to provide the necessary set-up time. The first technique, shown in Figure 19, takes advantage of the independence of the display WRITE cycle and the internal refresh cycle. In this case, data is written to the display on every microprocessor READ/WRITE cycle. A display WRITE signal is created by Nanding 0<sub>2</sub> with the microprocessor WRITE signal. Even though the display is being written during every microprocessor READ/WRITE cycle, the display message is unaffected since the data in the latches remains unchanged.

ing Critican a locid high to a logic low and back to a logic high without charging any other data. The CLOUR will remove cursors thim each location in the display. The texsubroutine will write a 16 character message from a table ocated in the mic ophocessor. Once the PIA has been domby changing the contents of the message table at microprocessor addressed 1900 to 090F or by changing the pointer tool. The design can control the display output by ion. The design can control the display output by

The I/G mapped system uses a peripheral internet admission (PIA). One method of using a PIA is to configure it as a intern. An alternate technique is to take advantage of the

Figure 20a. 6800 Microprocessor Interface Circuitry which Generates Adequate Display Hold Time by Delaying the Display Write Signal

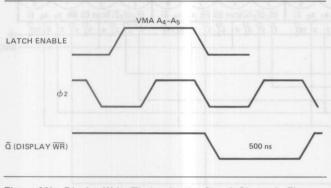

The other technique, illustrated in Figure 20, is to delay the display  $\overline{\text{WRITE}}$  pulse. This is accomplished by using 0<sub>2</sub> to clock a D-type flip-flop. A<sub>4</sub>-A<sub>15</sub> and VMA are connected to the D-input of the flip-flop. The  $\overline{\text{Q}}$  output of the flip-flop is used as the display  $\overline{\text{WRITE}}$ .

#### Using the Cursor, Blanking and Clear Functions

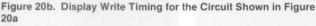

The CURSOR, BLANKING and CLEAR functions control the display output. To effectively use these display functions external storage of this information is required. However, if the designer only wants to display ASCII data, these inputs can be tied to their correct logic levels. Figure 21 shows how a latch can be organized to control these signals and the timing of the clock to the latch. The microprocessor address lines and WRITE signal can be used to locate the latch in microprocessor memory and to clock the latch.

Before using the display, the latch needs to be loaded with the appropriate control word to enter data. After data has been written into the display, the designer can control the display output by changing the contents of the latch. To ensure reliable operation of the display an EDGE TRIG-GERED LATCH MUST BE USED. The latch should be triggered on the rising edge of the microprocessor WRITE signal to guarantee that valid data is stored in the latch. Failure to meet this requirement can result in an erroneous CLEAR signal.

# **I/O MAPPED SYSTEM**

The I/O mapped system uses a peripheral interface adaptor (PIA). One method of using a PIA is to configure it as a latch. An alternate technique is to take advantage of the

Figure 21. Use of 74LS273 to Store Control Signals for the HPDL-2416  $\ensuremath{\mathsf{HPDL-2416}}$

PIA's handshaking capabilities to provide a display WRITE signal. Both configurations will be discussed.

# Latch Technique

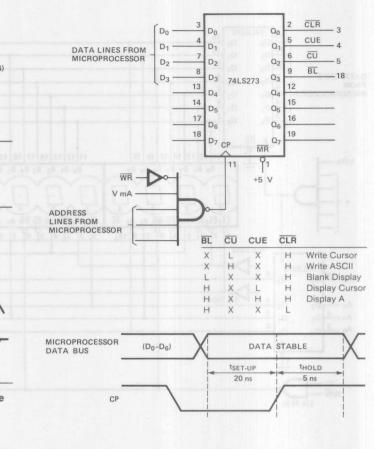

The schematic in Figure 22 shows how an 8255 PIA can be used to interface an HPDL-2416 to an 8085 microprocessor. Three output ports from the 8255 are used to write data to the HPDL-2416. Port A is used to store data, port B is used to store display function information and port C is used to store display address data.

Figure 23 lists four subroutines needed to control the display. Before the display can be used, the PIA has to be initialized. The INIT routine formats the PIA as three 8 bit output ports. Both the CLCUR and the TEXT subroutines use the WRITE subroutine to generate a display WRITE signal. A display WRITE is created by the software switching C7 from a logic high to a logic low and back to a logic high without changing any other data. The CLCUR will remove cursors from each location in the display. The text subroutine will write a 16 character message from a table located in the microprocessor. Once the PIA has been done by changing the contents of the message table at microprocessor addresses 0900 to 090F or by changing the pointer, TABLE+10H, in the text subroutine to a new message location. The designer can control the display output by changing the contents of port B after data has been written into the display.

Figure 22. 8255 PIA Interface to the HPDL-2416

| LOC<br>00<br>01<br>02<br>03<br>0900<br>0800<br>0810<br>0820<br>0840 | 0800<br>0810<br>0820    | SOURCE<br>PortA<br>PortB<br>PortC<br>Init<br>Table<br>Initial<br>Write<br>Clcur<br>Text | EQU<br>EQU<br>EQU<br>EQU<br>EQU | MENTS<br>00H<br>01H<br>02H<br>03H<br>0900H<br>0800H<br>0810H<br>0820H<br>0820H<br>0840H | influce to the HIPUL-2416                                                                                      |  |

|---------------------------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------|---------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|

| 0802                                                                | 3E 80                   | INITIAL                                                                                 | OUT                             | A,80H<br>INIT                                                                           | Initialize PIA as Three Output Ports                                                                           |  |

|                                                                     | D3 01                   |                                                                                         | OUT<br>RET                      | A,OSH<br>PortC                                                                          |                                                                                                                |  |

|                                                                     | F6 80                   | WRITE                                                                                   | ORI                             | A,80H                                                                                   | Load Address and Set WRITE Pin High.                                                                           |  |

| 0814                                                                | D3 02<br>E6 7F<br>D3 02 |                                                                                         | ANI                             | PortC<br>A,7FH<br>PortC                                                                 | Set HRITE pin low.                                                                                             |  |

|                                                                     | F6 80<br>D3 02          |                                                                                         | ORI<br>OUT<br>RET               | A,80H<br>PortC                                                                          | Set WRITE Pin High.<br>Hrite Cycle Complete.<br>Return.                                                        |  |

| 0820                                                                | 2E 00                   | CLCUR                                                                                   | MVI                             | A,OOH<br>PortA                                                                          | Select Cursor Memory and Set DO to O.                                                                          |  |

| 0826<br>0827<br>082A                                                | CD 100                  |                                                                                         | DCR                             | B,OFH<br>A,B<br>HRITE<br>B                                                              | Set Length of Hessage.<br>Howe Display Address To Acc.<br>Call HRITE Subroutine.<br>Decrement For Next Address |  |

| 082E                                                                | C2 260<br>78<br>CD 100  |                                                                                         | JNZ<br>MOV<br>CALL              | CLC<br>A,B<br>HRITE                                                                     | Loc O?, No Jump CLC, Yes Continue.<br>Clear Last Cursor Location.                                              |  |

| 0832                                                                | C9                      |                                                                                         | RET                             |                                                                                         | Return.                                                                                                        |  |

|                                                                     | 3E 05<br>D3 01          | TEXT                                                                                    | NVI<br>OUT                      | A,05H<br>PortB                                                                          | Set Display To Show ASCII                                                                                      |  |

|                                                                     | 06 00                   |                                                                                         | HUI                             | B,00H                                                                                   | Set Pointer To Right Most Character Loc                                                                        |  |

| 0849                                                                |                         | 9<br>NEXT                                                                               | MOV                             | H, TABLE+10H                                                                            | Load ASCII Data In PIA.                                                                                        |  |

| 084C                                                                | D3 00<br>79<br>CD 100   | 8                                                                                       | HOV<br>CALL                     | PortA<br>A,B<br>HRITE                                                                   | Move Character Address To Acc.<br>Call WRITE Subroutine                                                        |  |

| 0850<br>0851                                                        | 28<br>04                |                                                                                         | DCX                             | H                                                                                       | Decrement Pointer<br>Increment To Next Display Address.                                                        |  |

| 0854                                                                | 3E 10<br>B8<br>C2 480   | 0                                                                                       | HVI<br>CMP                      | A,10H<br>B                                                                              | End Of Message, Yes Continue;                                                                                  |  |

| 0858                                                                | 3E 05<br>D3 01          | D                                                                                       | JNZ<br>HVI<br>OUT<br>RET        | NEXT<br>A,OSH<br>PortB                                                                  | No, Jump To NEXT.<br>Set Display Control.<br>Return.                                                           |  |

Figure 23. 8085 Microprocessor Program to Interface to the Circuit in Figure 22

Figure 24. 6821 PIA to Interface to the HPDL-2416

| Location | Object<br>Code | Source<br>Statements | 10 1995) | 10 985 tarlar |

|----------|----------------|----------------------|----------|---------------|

|          | 0F 31          | Control A            | EQU      | \$ 0F 31      |

|          | 0F 30          | DDA                  | EQU      | \$ OF 30      |

|          | 0F 30          | PortA                | EQU      | \$ OF 30      |

|          | 0F 33          | Control B            | EQU      | \$ OF 33      |

|          | 0F 32          | DDB                  | EQU      | \$ 0F 32      |

|          | 0F 32          | Port B               | EQU      | \$ OF 32      |

|          | 05 00          | Init                 | EQU      | \$ 0500       |

|          |                |                      |          |               |

|          |                | .ani - tas           | ORG      | \$ 0500       |

| 0500     | 86 00          | Init                 | LDA A    | 1, \$00       |

| 0502     | C6 FF          |                      | LDA B    | I, \$FF       |

| 0504     | B7 0F 31       |                      | STA A    | E, Control A  |

| 0507     | F7 0F 30       |                      | STA B    | E, DDA        |

| 050A     | B7 0F 33       |                      | STA A    | E, Control B  |

| 050D     | F7 0F 32       |                      | STA B    | E, DDB        |

| 0510     | 86 2C          |                      |          | I, \$2C       |

| 0512     | B7 0F 31       |                      | STA A    | E, Control A  |

| 0515     | B7 0F 33       |                      |          | E, Control B  |

| 0518     | 39             |                      | RST      | W. Street and |

Figure 25. Program to Initialize a 6821 PIA.

#### Handshaking Technique

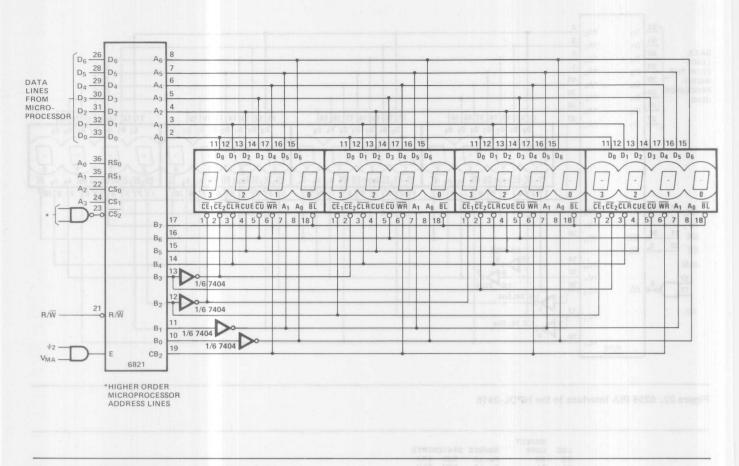

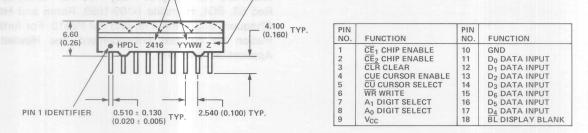

The circuit in Figure 24 is designed to use a 6821 PIA as an interface between a 6800 microprocessor and an HPDL-2416. The PIA requires a minimum of four microprocessor address locations, with two addresses for each port. The PIA has to be initialized before it can be used. Figure 25 shows how the PIA must be initialized to operate the circuit in Figure 24. Ports A and B are set up as outputs.

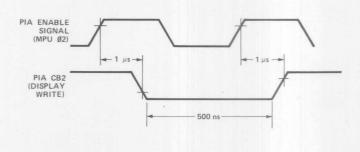

The 6821 PIA is configured to generate a display  $\overline{\text{WRITE}}$  signal every time display control information is written into port B. This eliminates the need for a  $\overline{\text{WRITE}}$  subroutine. Ports A and B have data bits assigned as shown in Figure 26. Table 1 shows how the output of port B controls the display system. Figure 27 shows the timing between the PIA enable and CB2 (display  $\overline{\text{WRITE}}$ ).

# **Control Register Configuration for Port A**

|                |                | Micropro       | cessor Dat     | a Bus Co       | nfiguration    |                |                |                                                  |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|--------------------------------------------------|

| D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | ocation Code Statementa                          |

| CR7            | CR6            | CR5            | CR4            | CR3            | CR2            | CR1            | CR0            | 6821 Port A Control Register<br>Designation      |

| Х              | X              | Х              | X              | X              | 1030 1         | X              | X              | Port A is selected                               |

| Х              | X              | X              | X              | X              | 0 060          | Х              | Х              | Data direction register of<br>Port A is selected |

# **Control Register Configuration for Port B**

|                |                | Micropro       | cessor Dat     | ta Bus Cor     | nfiguration    | nida           | a xai | DEAS C.C.E. BEDD                                            |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-------|-------------------------------------------------------------|

| D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | Do    | 3555 AG 00 NCHAR                                            |

| CR7            | CR6            | CR5            | CR4            | CR3            | CR2            | CR1            | CR0   | 6821 Port B Control Register<br>Designation                 |

| x              | Х              | 1              | 0              | 1              | 1080           | X              | X     | Port B selected to provide<br>a write pulse to the display. |

| Х              | X              | X              | X              | X              | 0              | X              | Х     | Data direction register B is selected.                      |

# 6821 A and B Port Bit Assignment

|                |                | Micropro       | cessor Dat     | a Bus Con      | figuration     |                |                |                                           |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-------------------------------------------|

| D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | nre 28. 9300 Microprocessor Sabroutine to |

| A7             | A <sub>6</sub> | A5             | A4             | A3             | A <sub>2</sub> | A1             | Ao             | Port A Data Register Designation          |

| Х              | D <sub>6</sub> | D <sub>5</sub> | D4             | D <sub>3</sub> | D <sub>2</sub> | D1             | D <sub>0</sub> | Port A Display Data                       |

regura 28 ista a subroutine capable of operating a 16 char- select the desire massage through a binary weighted input

| (nare) Rou     | and a col            | Microproc             | cessor Dat            | a Bus Con                         | figuration                        |                | - Carlos       | indi tea cuidan artina antina anti 1 antista id            |

|----------------|----------------------|-----------------------|-----------------------|-----------------------------------|-----------------------------------|----------------|----------------|------------------------------------------------------------|

| D <sub>7</sub> | D <sub>6</sub>       | D <sub>5</sub>        | D <sub>4</sub>        | D <sub>3</sub>                    | D <sub>2</sub>                    | D <sub>1</sub> | D <sub>0</sub> | ine 24 shows now to regarize a mes                         |

| B7<br>BL       | B <sub>6</sub><br>CU | B <sub>5</sub><br>CUE | B <sub>4</sub><br>CLR | B <sub>3</sub><br>CE <sub>2</sub> | B <sub>2</sub><br>CE <sub>1</sub> | B1<br>A1       | Bo<br>Ao       | Port B Data Register Designation<br>Port B Display Control |

validation to alcada to transmission research

# Figure 26. Configuration of the 6821 PIA

Table 1.

| <b>B</b> <sub>7</sub> | B <sub>6</sub> | <b>B</b> <sub>5</sub> | B <sub>4</sub> | B <sub>3</sub> | B <sub>2</sub>  | B <sub>1</sub> | B <sub>0</sub> |                                       |

|-----------------------|----------------|-----------------------|----------------|----------------|-----------------|----------------|----------------|---------------------------------------|

| BL                    | CŪ             | CUE                   | CLR            | CE2            | CE <sub>1</sub> | A <sub>1</sub> | A <sub>0</sub> | Port B Bits                           |

| 0                     | 0              | 0                     | 0              | X              | X               | X              | X              | Blank display & write cursor          |

| 0                     | 0              | 0                     | 1              | X              | X               | X              | X              | Blank display & write cursor          |

| 0                     | 0              | 1                     | 0              | X              | X               | X              | X              | Blank display & write cursor          |

| 0                     | 0              | 1                     | 1              | X              | X               | X              | X              | Blank display & write cursor          |

| 0                     | 1              | 0                     | 0              | X              | X               | X              | X              | Blank display & write ASCII data      |

| 0                     | 1              | 0                     | 1              | X              | X               | X              | X              | Blank display & write ASCII data      |

| 0                     | 1              | 1                     | 0              | X              | X               | X              | X              | Blank display & write ASCII data      |

| 1                     | 0              | 0                     | 0              | X              | X               | X              | X              | Use only to clear display             |

| 1                     | 0              | 0                     | 1              | X              | X               | X              | X              | Write cursor & display ASCII data     |

| 1                     | 0              | 1                     | 0              | X              | X               | X              | X              | Use only to clear display             |

| 1                     | 0              | 1                     | 1              | X              | X               | X              | X              | Write cursor & display cursor         |

| 1                     | 1              | 0                     | 0              | X              | X               | X              | X              | Use only to clear display             |

| 1                     | 1              | 0                     | 1              | X              | X               | X              | X              | Write ASCII data & display ASCII data |

| 1                     | 1              | 1                     | 0              | X              | X               | X              | X              | Use only to clear display             |

| 1                     | 1              | 1                     | 1              | X              | X               | X              | X              | Write ASCII data & display cursor     |

X = Do Not Care

1 = Logic High

0 = Logic Low

simply wishes to display one of several fixed status messages. While a microprocessor can be dedicated to this application, microprocessor time and memory are required Microprocessor inferraction can be minimized by using a display interface which includes all circuitry needed for text

Figure 27. Display Write Timing for the 6821 PIA Circuit Shown in Figure 24

| Location | Object<br>Code | Source<br>Statements | D, Do           | noit | Location | Hex<br>Data | Characte | er | D <sub>8</sub> | 07           |

|----------|----------------|----------------------|-----------------|------|----------|-------------|----------|----|----------------|--------------|

| Tett     | 0F 30          | Port A               | EQU \$ 0F30     | S    | 0600     | 42          | В        |    | Left Most      | Character    |

|          | 0F 32          | Port B               | EQU \$ 0F32     |      | 0601     | 55          | U        |    |                |              |

|          | 06 00          | Table                | EQU \$ 0600     |      | 0602     | 59          | Y        |    |                |              |

|          | on register of | Darn diffecti        |                 |      | 0603     | 20          | Space    |    |                |              |

|          | acted          | PortA is se          |                 |      | 0604     | 48          | Н        |    |                |              |

|          |                |                      |                 |      | 0605     | 50          | Р        |    |                |              |

|          |                |                      | ORG \$ 0550     |      | 0606     | 20          | Space    |    |                |              |

| 0550     | C6 DF          |                      | LDA B I, \$DF   |      | 0607     | 44          | D        |    |                |              |

| 0552     | CE 0600        |                      | LDX Table       | noit | 0608     | 49          | property |    |                |              |

| 0555     | A6 00          | NCHAR                | LDA A X, \$00   |      | 0609     | 53          | S        |    |                |              |

| 0557     | B7 0F 30       |                      | STA A E, Port A |      | 060A     | 50          | P        |    |                |              |

| 055A     | F7 0F 32       | - 6821 Port B        | STA B E, Port B | 2    | 060B     | 46          | L        |    |                |              |

| 055D     | 5A             | De-qualitan          | DEC B           | 1000 | 060C     | 41          | A        |    |                |              |

| 055E     | 08             | Dense Hillom         | INX             |      | 060D     | 59          | Y        |    |                |              |

| 055F     | C1 CF          | aluq ottak 6         | CMP BI, \$CF    |      | 060E     | 49          | S        |    |                |              |

| 0561     | 26 F2          | SDORED BU            | BNE NCHAR       |      | 060F     | 20          | Space    |    | Right Mos      | st Character |

| 0563     | 39             | is s lected.         | RTS             | 1    |          |             |          |    | 5              |              |

Figure 28. 6800 Microprocessor Subroutine to Write a 16 Character Message via a 6821 PIA

Figure 29. Message Table for 6800 Microprocessor Subroutine Listed in Figure 28

Figure 28 lists a subroutine capable of operating a 16 character display. The subroutine works as follows:

Figure 29 shows how to organize a message table for the subroutine listed in Figure 28.

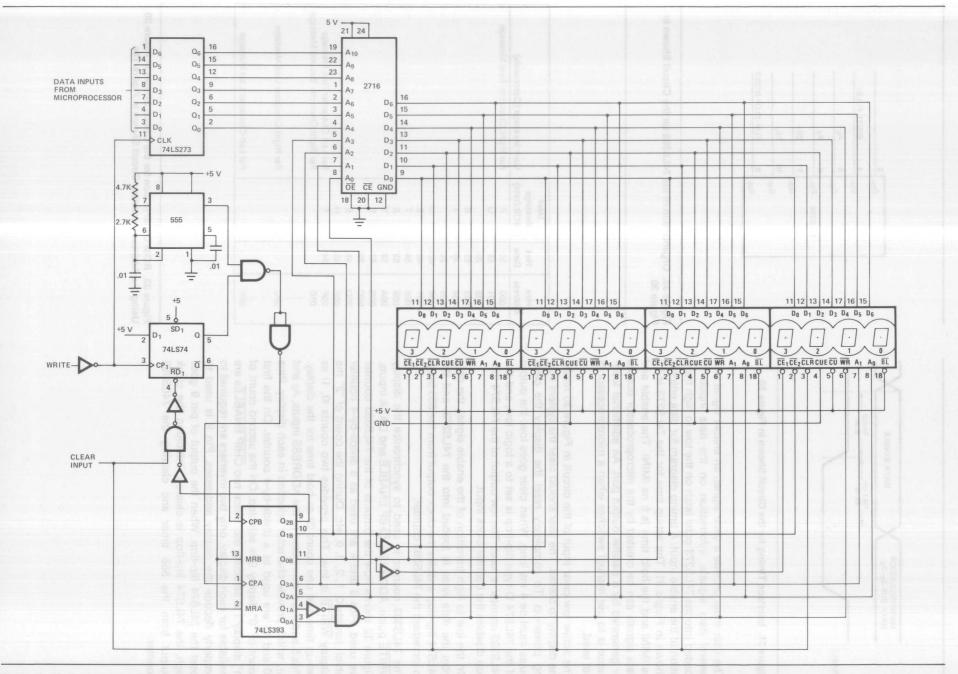

# PREPROGRAMMED MESSAGE

There are many occasions when a designer needs to use an alphanumeric display. In some applications, the designer simply wishes to display one of several fixed status messages. While a microprocessor can be dedicated to this application, microprocessor time and memory are required. Microprocessor interaction can be minimized by using a display interface which includes all circuitry needed for text generation. Then, the microprocessor simply needs to

select the desired message through a binary weighted input. This type of display interface is called a preprogrammed message system. The preprogrammed message system appears to the microprocessor as a very fast write only memory which uses only one memory location.

The circuit in Figure 30 is designed as a preprogrammed message system. The system shown is capable of displaying 128 different character messages that are 16 characters in length. The system can be modified to operate with different character lengths by varying the length of the counters and ROM size. The microprocessor selects a preprogrammed message to be displayed by using a binary weighted code. The system then feeds the message to be displayed to the HPDL-2416 one character at a time.

18

Figure 30. Preprogrammed Message System

19

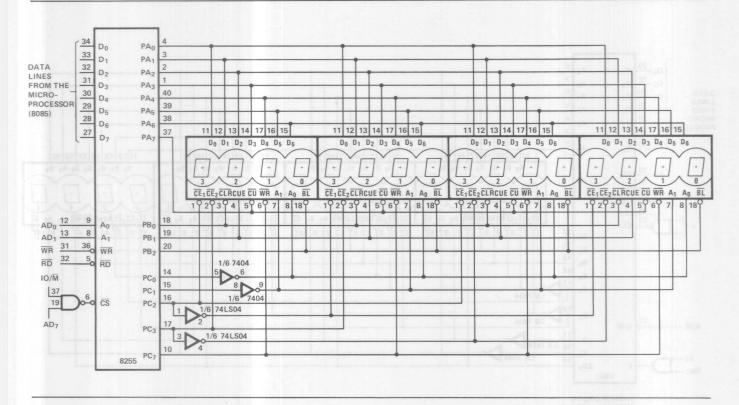

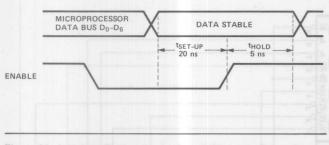

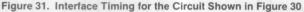

The user must provide a clear signal, an enable signal and several data signals. Information on the data inputs is loaded into the 74LS273 octal latch on the low to high transition of the enable input. A timing diagram for data entry is shown in Fiugre 31. The set-up time for the 74LS273 is 20 ns (MIN) and the hold time is 5 ns (MIN). The enable and data signals can be created by the microprocessor busses or generated by a parallel output port. An additional technique is to use manual switches when a microprocessor is not used.

The active low clear input of the circuit in Figure 30 resets the display to blanks. The user should clear the system during power-up. To completely reset the display the clear pulse must be 4 ms long. When clear goes low, the output of the 74LS74 D-type flip-flop is set to a logic low, and the 74LS393 counter is reset. The low output of the 74LS74 flipflop disables the counter clock input.

On the low to high transition of the enable signal, the data from the data lines is loaded into the 74LS273, and the 74LS74 flip-flop enables the clock output from the 555 timer to increment the 74LS393 counter.

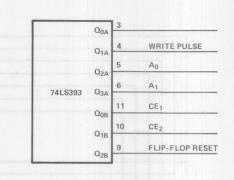

The 74LS393 counter is used to synchronize the display WRITE pulse, ADDRESS, CHIP ENABLE and DATA inputs. Figure 32 shows how the outputs of the 74LS393 counter are used. Pins 3 and 4 are used as a divide-by-4 counter which counts 0, 1, 2, 3, 0, etc. During the count of "2" the display WRITE is low. This provides two counts (0, 1) as set-up time and one count (3) as hold time for the display. Pins 5 and 6 are connected to the ADDRESS inputs, Ao and A1, which provide character selection in each display. Pins 10 and 11 are used as a divide-by-4 counter. On the first count of "0" display 0 is selected. On the second count of "1" display 1 is selected, etc. Since two CHIP ENABLEs are available for each display, only two inverters are required to properly decode the display addresses. Pin 9 is used to reset the 74LS74 flip-flop. When the output of pin 9 goes high, the 74LS74 flip-flop is cleared, inhibiting the clock output from the 555 timer and clearing the 74LS393 counter.

Figure 32. Organization of the 74LS393 for the Circuit Shown in Figure 30

| Hex<br>Address | Hex<br>Data | User<br>Message<br>(ASCII Data) | User Message (Comments)            |

|----------------|-------------|---------------------------------|------------------------------------|

| 000            | 50          | Р                               | Far Right Character First Message  |

| 001            | 55          | U                               |                                    |

| 002            | 20          |                                 |                                    |

| 003            | 53          | S                               |                                    |

| 004            | 49          | I                               |                                    |

| 005            | 20          |                                 |                                    |

| 006            | 4D          | M                               |                                    |

| 007            | 45          | E                               |                                    |

| 800            | 54          | Т                               |                                    |

| 009            | 53          | S                               |                                    |

| 00A            | 59          | Y                               |                                    |

| 00B            | 53          | S                               |                                    |

| 00C            | 20          | Land B. Mar                     |                                    |

| 00D            | 45          | E                               |                                    |

| 00E            | 48          | Н                               |                                    |

| 00F            | 54          | Т                               | Far Left Character First Message   |

| 010            |             |                                 | Far Right Character Second Message |

|                |             |                                 |                                    |

| : .            |             |                                 |                                    |

| 3F0            |             |                                 | Far Right Character Last Message   |

|                |             |                                 |                                    |

| :              |             |                                 |                                    |

| 3FF            |             | _                               | Far Left Character Last Message    |

Figure 33. ROM Organization for the Circuit Shown in Figure 30 Using the Address Decoding Circuit Shown in Figure 14a

| Hex<br>Address | Hex<br>Data | User<br>Message<br>(ASCII Data) | User Message (Comments)               |

|----------------|-------------|---------------------------------|---------------------------------------|

| 000            | 54          | Т                               | Far Left Character First Message      |

| 001            | 48          | Н                               | D region of a more summing            |

| 002            | 45          | SUL E VOI                       | un Auguuni e un sesarou ue            |

| 003            | 20          | neg egeneve                     | does NOT eliminate ESO. The           |

| 004            | 53          | S                               | caive and tSC voltage of les          |

| 005            | 59          | Y                               | water new country wheel designs his   |

| 006            | 53          | S                               | But Budirth read and the substance    |

| 007            | 54          | T                               | pamab bini .V. kot Vi 6 harti         |

| 800            | 45          | E                               | mese lower volta pos                  |

| 009            | 4D          | M                               | and the second second second          |

| 00A            | 20          | an an an                        | Real montheyand US3 to longoo         |

| 00B            | 49          | 1                               | rules:                                |

| 00C            | 53          | S                               | Rute No. 1: T. c al electroni         |

| 00D            | 20          | parties controlled -            | and the second states a second states |

| 00E            | 55          | U                               | PARTE PARTE PARTE                     |

| 00F            | 50          | Р                               | Far Right Character First Message     |

| 010            |             |                                 | Far Left Character Second Character   |

| storement.     | ge an       | and a store                     | Rule No. 3: Pec. Ige perts prop.      |

| 03F            | etite       | am, cond                        | Far Left Character Last Message       |

| :<br>3FF       |             |                                 | Far Right Character Last Message      |

Figure 34. ROM Organization for the Circuit Shown in Figure 30 Using the Address Decoding Circuit Shown in Figure 14b

The organization of the 2716 EPROM depends on the display format. If the display is formatted as shown in Figure 14a, the EPROM is organized as shown in Figure 33. However, if pins 5 and 6 of the 74LS393 counter are inverted, the display is formatted as shown in Figure 14b and the EPROM is organized as shown in Figure 34. The 74LS273 latch selects the message to be displayed through the higher order address inputs of the EPROM.

# MECHANICAL AND ELECTRICAL HANDLING

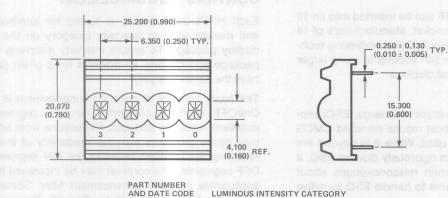

The HPDL-2416 can be stacked horizontally and vertically to create messages of any size. Figure 35 shows the package dimensions for the part. The display is designed to operate continuously from -20°C to +70°C for all possible input conditions (including the illuminated cursor in all four character locations).

LUMINOUS INTENSITY CATEGORY

NOTES

1. UNLESS OTHERWISE SPECIFIED, THE TOLERANCE ON ALL DIMENSIONS IS 0.254 mm (0.010 IN.) 2. DIMENSIONS IN mm (INCHES).

#### Soldering and Post Solder Cleaning

The HPDL-2416 may be hand soldered or wave soldered with SN63 solder. Hand soldering may be safely performed only with an electronically temperature controlled soldering iron that is securely grounded. For best results, the iron tip temperature should be set at 315°C ( $600^{\circ}$ F). For wave soldering, a rosin based RMA flux or a water soluable organic acid (OA) flux can be used. The solder wave temperature should be 245°C  $\pm$ 5°C (473°F  $\pm$ 9°F), and the dwell in the wave shoud be between 1 1/2 to 3 seconds for optimum soldering. Preheat temperature should not exceed 93°C (200°F) as measured on the solder side of the PC board.

Post solder cleaning may be performed with a solvent or aqueous process. For solvent cleaning, Allied Chemical Genesolv DES, Baron Blakeslee Blaco-Tron TES or Du Pont Freon TE can be used. These solvents are azeotropes of trichlorotrifluroethane FC-113 with low concentrations of ethanol (5%). The maximum exposure time in the solvent vapors at boiling temperature should not exceed 2 minutes. Solvents containing high concentrations of alcohols, pure alcohols, isopropanol or acetone should not be used as they will chemically attack the nylon lens. Solvents formulated with trichloroethane FC-111 or FC-112, and trichloroethylene (TCE) are not recommended.

An aqueous cleaning process is highly recommended. A saponifier, such as Kester Bio-kleen Formula 5799 or equivalent, may be added to the wash cycle of an aqueous process to remove to remove rosin flux residues. Organic acid flux residues must be thoroughly removed by an aqueous cleaning process to prevent corrosion of the leads and solder connections. The optimum water temperature is 60°C (140°F). The maximum cumulative exposure if the HPDL-2416 to wash and rinse cycles should not exceed 15 minutes.

#### **Socketing Considerations**

The Hewlett-Packard HPDL-2416 can be inserted into an 18 pin 15.24 mm (0.600 inch) DIP socket. Manufacturers of 18 pin DIP sockets are listed in table 2. Other socketing techniques including using two 9 pin SIP sockets or using larger DIP sockets, that can hold several displays.

#### **Handling Considerations**

The HPDL-2416 has an electro-static discharge (ESD) protected CMOS IC; however, for best results standard CMOS handling precaution should be used. While it is beyond the scope of this application note to rigorously discuss ESD, it is useful to discuss two common misconceptions about ESD and some simple procedures to handle ESD sensitive devices. The first misconception is that only unmounted components are susceptible to ESD. Unless a circuit board is properly protected, mounting the component in a PC board can increase the risk of ESD damage. The traces allow the discharge to be conducted to more than one part and provide additional discharge points.

The second misconception is that only low humidity environments allow the production of ESD. While the fact is true an increase in the humidity will lower the ESD voltage, it does NOT eliminate ESD. The average person will not perceive and ESD voltage of less than 3 kV to 4 kV. The voltages encountered during high humidity are typically less than 3 kV to 4 kV, and damage to the part can occur at these lower voltages.

Control of ESD prevention centers on the following basic rules:

**Rule No. 1:** Treat all electronic parts and assemblies as static sensitive.

**Rule No. 2:** Handle all sensitive parts and assemblies at "Static-Safe work stations."

**Rule No. 3:** Package parts properly for storage or transportation by using conductive foam, conductive tubes or conductive bags.

#### **Table 2. Socket Manufacturers**

| Aries                | Samtec               |

|----------------------|----------------------|

| Electronics, Inc.    | Electronic Hardware  |

| P.O. Box 130         | P.O. Box 1147        |

| Frenchtown, NJ 08825 | New Albany, IN 47150 |

| (201) 996-6841       | (812) 944-6733       |

|                      |                      |

# **CONTRAST ENHANCEMENT**

Each HPDL-2416 display is tested for luminous intensity and marked with an intensity category on the side of the display package. To ensure intensity matching for multiple package applications, all displays for a given panel should have the same category.

The basic concept of contrast enhancement is to improve ON/OFF segment contrast. The OFF segments provide excellent reflective surfaces. Reflections from ambient light may cause problems with the readability of the display by reducing the contrast between the ON segments and the OFF segments. The contrast may be increased by using the appropriate contrast enhancement filter. Some suggested filters are Panelgraphic Ruby Red 60, Panelgraphic Dark Red 63, SGL Homalite H100-1650, Rohm and Haas 2423, Chequers Engraving 118, and 3M R6510. For further information on contrast enhancement, see Hewlett-Packard Application Note 1015.