### **Power Supply Design**

Separate analog and digital power supplies and grounds are needed for good low noise performance of the CMOS imaging device. It is important to keep the analog and digital sections of a camera circuit separate. Noise on the analog supply and ground can degrade the performance of the image. Low light performance will be greatly improved by following careful power supply design rules.

### Grounding

A "star" ground is recommended. The designer should evaluate the power supply design and locate a stable ground point. This is usually at the battery or the largest bypass capacitor on the pre-regulated input voltage. On a camera with an external power supply, or a USB powered device, the best ground is usually located at the incoming connector ground pin. Several grounds should be connected to this point in a star pattern. Keeping the analog and digital grounds separate and only connected at this single point will improve isolation. Resistors or inductors between analog and digital ground are not recommended. A low impedance and quiet ground will give best results.

# **Power Supply Considerations with CMOS Imagers** Application Note 1219

Digital V<sub>dd</sub>

This voltage is not too critical and usually can be shared with other circuitry in the design.

# Analog V<sub>dd</sub>

This supply must be kept separate and quiet. A separate regulator should be used. This will provide the best isolation. The Analog V<sub>dd</sub> should not be derived from the digital V<sub>dd</sub>. Trying to use the digital V<sub>dd</sub> by filtering with a series/parallel RCL circuit will not provide the necessary isolation. A good voltage regulator will provide the isolation needed. A low frequency bypass capacitor (e.g. 4.7  $\mu$ F) and a high frequency bypass capacitor  $(0.01 \ \mu F)$  will keep the supply quiet. Check the supply on an oscilloscope. Changing the persistence of the scope to infinite will help one see high and low frequency noise and ripple.

# **Image Artifacts**

Since the CMOS imager is clocked row-by-row, any power supply variations will be sampled and cause a row-by-row offset voltage. Offset voltage variations will appear in the image as differences in brightness. If random horizontal lines of various brightness appear in the image, this is usually caused by a noisy or unregulated analog V<sub>dd</sub> supply. Try increasing the bypass capacitor value to see if the image improves. If evenly spaced horizontal bands are seen this might be due to power supply ripple or florescent light flicker. Power supply ripple is corrected by filtering the incoming preregulated voltage. Light flicker is corrected by choosing an exposure time that is a multiple of 60 Hz (50 Hz for non-US applications).

# **Power Supply Example**

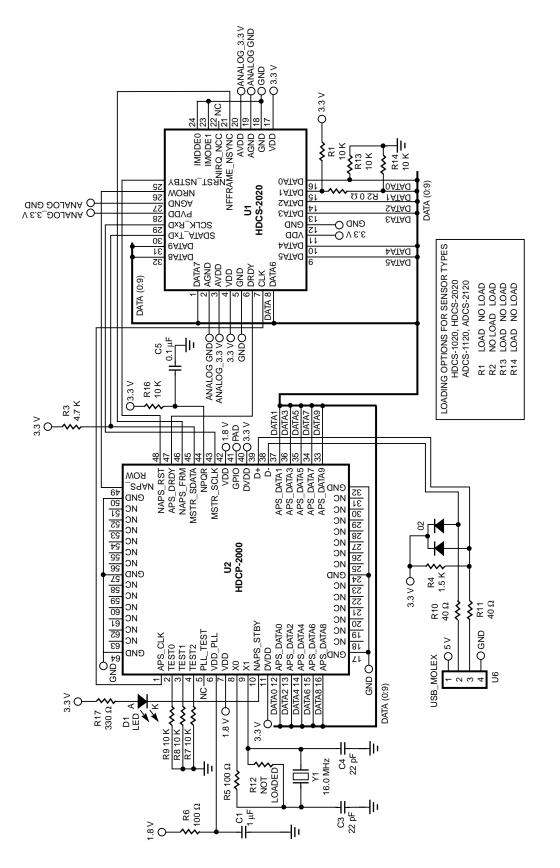

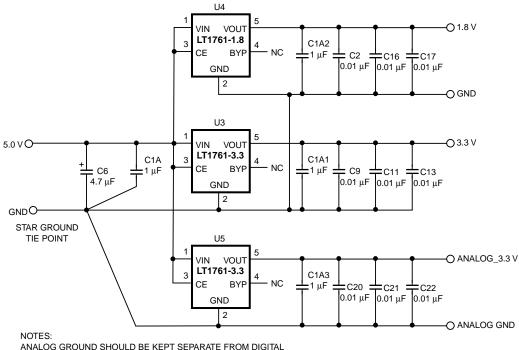

This example is for a USB powered device. Since the incoming power is external the best ground will be located at the USB connector. This location is the base of our "star" ground. A 4.7 µF capacitor located next to the connector helps quiet the incoming +5 VDC. Three terminal regulators are used in this design. The Agilent circuit requires +3.3 VDC and +1.8 VDC to operate the digital section of the camera. A common digital ground is used. It is not a good idea to run separate digital grounds in a star. A single digital ground plane is the best. A separate regulator is used to generate +3.3 VDC for the analog section of the CMOS imager. The analog ground in this case is a star ground referenced back to our incoming power. Splitting a ground plane in a

Figure 1. Agilent Technologies HDCE-1020 / 2020 and ADCE-1120 / 2120 Demo Board

PC board layout can be an easy way to route a low impedance ground for the analog supply. The low quiescent current regulators used here required a minimum of 1  $\mu$ F on the output of these devices for good regulation. Follow the recommended design rules for the parts you design with. A good solid ceramic 1  $\mu$ F capacitor will do a good job of both low and high frequency bypassing.

ANALOG GROUND SHOULD BE KEPT SEPARATE FROM DIGITAL GROUND AND TIED TOGETHER AT THE STAR GROUND TIE POINT.

Figure 2. Agilent Technologies HDCE-1020 / 2020 and ADCE-1120 / 2120 Demo Board.

www.semiconductor.agilent.com

Data subject to change. Copyright © 2001 Agilent Technologies, Inc. Obsoletes 5988-2354EN September 7, 2001 5988-4072EN

Agilent Technologies