|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         | Agilent 09600 Vector Signal Analyzer                                         |                                                                                                                                                                                    | <u></u>                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Colorer Sector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                         | File Edit Control Sparce Input TestSietup MeasSetup Display In               | ace Markers Utilities Help                                                                                                                                                         |                                  |

| Advectings Madure ( 2 / Julie for paths of ) (Privates 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SPALL L L L L L L L L                   | • II • 🕼 🕲 🕲 🕲 🗇 🗇 🖉 • 🖡 🕻                                                   | 🗆 🔹 🔢 🚹 🧧 50%. Oxfor Normal 🔹                                                                                                                                                      |                                  |

| Control of the last last last last and last last last last last last last last                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                         | ACD11 MEKT Mean Tree Range, 1 V                                              | C. Chit MSK1 En Vert Time Range, 1 V                                                                                                                                               | E Ch1MSK1MeanTime Range, 1 V     |

| Mail         Mail <th< th=""><th></th><th>HQ</th><th>LinMeg</th><th>HÉye</th></th<> |                                         | HQ                                                                           | LinMeg                                                                                                                                                                             | HÉye                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         | 300                                                                          |                                                                                                                                                                                    | 38                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         | -15                                                                          |                                                                                                                                                                                    | 45                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Signal Extractor for DigRF              | × m 17100                                                                    |                                                                                                                                                                                    | Stat: -1 sym Stop: 1 sym         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Input Bus/Signal                        | 1 Spectrum Planger 10 dBm                                                    | D: Orl MSK1 SynovEm Range: 1 V<br>M = 623.34 mSzma<br>2007 X pk at sym 25<br>gg = 2,7551 m3zma                                                                                     | E Chil MSK1 Meas Time Range: 1 V |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | RxTx Data                               |                                                                              | g218 = 1cb 31 means 78<br>1.12 satc kit sym 78<br>satc kit = 51325 modeg<br>732 moleg kit sym 25<br>sitc = 252276 seltz<br>005tet = -72248 d8                                      | Q.E.M                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 🗐 Start Sample 🛛 🔲 — 🗄                  |                                                                              | ad Ev = 96.940 mdeg<br>in Imb = 0.024 dB                                                                                                                                           | Re 2                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | End Sample 1000                         | r 0 Hz Spar: B45 33 Hz<br>5 S1111 Hz Tender: 57 25 Kor                       | 0 11001011 01100011 00000001 10011110<br>22 0110111 1101010 11011011 00000101<br>64 1111100 11010110 10110010<br>95 00110010 10101100 1110010 10011011<br>28 0011010 11011011 0010 | -1.5<br>Start -1 spm Step: 1 spm |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Extractor Algorithm                     | 1971 25 57% 1<br>1987: 25 57% 1.3<br>1987: 25 87% 1<br>1987: 23 87% - 7152.7 | -139.4416 dag                                                                                                                                                                      |                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | File Name: DigRF_1_12_Trig_Qual2.xml    | 1011 24 1798 -610.3                                                          | 348 a                                                                                                                                                                              |                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Algorithm: DigRF 1.12 Trigger Qualified |                                                                              |                                                                                                                                                                                    |                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Load Algorithm                          |                                                                              |                                                                                                                                                                                    |                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | OK Cancel He                            |                                                                              |                                                                                                                                                                                    |                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         |                                                                              |                                                                                                                                                                                    |                                  |

## Making RF Measurements on Digital Serial Data with Agilent's Signal Extractor and the 89601A Vector Signal Analyzer

Application Note 1593

## **Table of Contents**

| Introduction       3         Digital signals replacing analog       5         Interfaces changes       5         Serial or parallel?       7                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Measurement Basics       7         Logic analyzer basics       7         Vector signal analyzer basics       9         What kinds of measurements do we need?       9         Signal integrity measurements       11                                                                                 |

| The B4602A Signal Extractor Tool       12         Extracting the data       12         Understanding the algorithm       14                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                      |

| Setting up the Logic Analyzer with Signal Extractor and the 89601A Software22Getting started22Logic analyzer23Setting up the logic analyzer23Logic analyzer results30Vector signal analyzer33Setting up the vector signal analyzer33Vector signal analyzer results33Vector signal analyzer results33 |

| Getting started22Logic analyzer23Setting up the logic analyzer23Logic analyzer results30Vector signal analyzer33Setting up the vector signal analyzer33                                                                                                                                              |

| Getting started22Logic analyzer23Setting up the logic analyzer23Logic analyzer results30Vector signal analyzer33Setting up the vector signal analyzer33Vector signal analyzer results33Vector signal analyzer33Setting up the vector signal analyzer33Settor signal analyzer results39               |

### Introduction

This application note is designed to guide you through making measurements on serial data using an Agilent logic analyzer with the B4602A Signal Extractor tool and Agilent's 89601A vector signal analyzer (VSA) software. Specifically, we will look at the serial IQ interfaces from a DigRF 1.12 signal and use a preset algorithm from the B4602A tool to extract the IQ data for demodulation and logic analysis. Whether you are a digital engineer faced with making RF-type measurements or an RF engineer trying to make digital measurements, this note will help you understand how to accomplish your measurement goal.

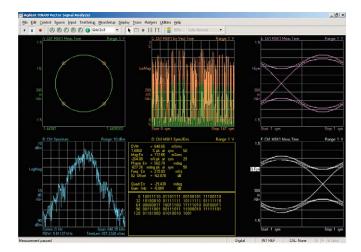

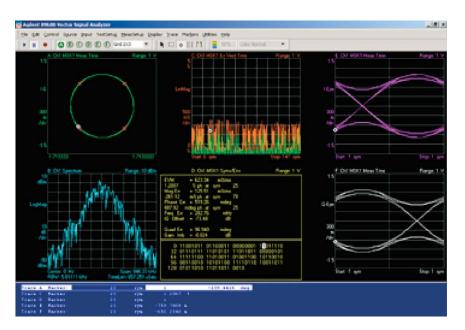

Figure 1. 89601A vector signal analysis software gives you multiple ways to view your data.

#### Introduction

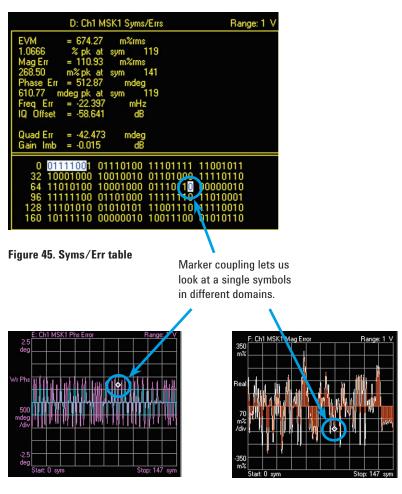

The vector signal analyzer is a powerful tool for time, frequency and modulation domain measurements. Modulation domain measurements such as EVM, constellation and eye diagrams give you a good look at what your devices are really doing. Error vector time displays offer you insight into such things as filtering problems, distortion and frequency errors. Eye diagrams show you symbol timing that can reveal errors in clocking. The symbols/error summary table gives you a variety of information including IQ offset, phase, and magnitude error as well as EVM – it even shows you which symbols are causing the most trouble. For pulsed signals, you can look at pulse shape and timing. In all cases, you can directly correlate between the logic and RF measurements for digital IQ signals.

The logic analyzer tells you quite a bit, too. Are the levels correct? Are the right number of bits there and are they in the correct order? The logic analyzer allows you to directly correlate the data sent with the data received. You also can switch to timing mode to ensure the edges of clocks and bits are lined up correctly. Using the VSA with the logic analyzer allows you to check the accuracy of the modulator, filters and more.

| GdArea Usace measurements           Sock         200 molds         101 million         100 million <th>) 🖉 🖬 🕾 🛤 🤅</th> <th>H T H Q Q</th> <th>*    臣 提 155</th> <th></th> <th>14.7</th> <th>► 🕸 🔳 🖾</th> <th></th> <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ) 🖉 🖬 🕾 🛤 🤅      | H T H Q Q              | *    臣 提 155 |                          | 14.7              | ► 🕸 🔳 🖾 |                              |                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------|--------------|--------------------------|-------------------|---------|------------------------------|-----------------|

| Burding at<br>Burding at<br>Enclands         Bit with a set of the set of                                                                                                                                                                                                                                                                                                                              |                  |                        | d            | ick here to insert new m | easurements       |         |                              |                 |

| Burblevit         300 m         100 m         200 m         200 m         200 m         200 m         200 m         21 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m         1 m <th>Scale 200 ns/div</th> <th>E tit tit Delay</th> <th>900 ns</th> <th>H T</th> <th>M</th> <th></th> <th></th> <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Scale 200 ns/div | E tit tit Delay        | 900 ns       | H T                      | M                 |         |                              |                 |

| Image: Contraction         Image:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |                        |              | -                        | 100               |         |                              |                 |

| Image: Control of the contro                                                                                                                                                                                                                                                                                                                           | Bus/Signal       | -300 nz -100 nz 100 nz | 300 Nr 500   | NE 700 NE 91             | 1.1 us<br>T i i l | 1,3 w   | 1.5 us 1.7 us 1.9 us 2.1<br> | us<br>  1 1 1   |

| Time         2,2 bits           B-Wyourd         eld 1111 1110 (00)         016 101 1101 1101 1101 (00)           B-Wyourd         eld 1111 110 (00)         016 101 101 1101 1101 (00)           Myourd         1100 6010 0001 0000         1101 1011 1011 1011 (00)           Mybus 00         0         1           Mybus 01         0         1           Mybus 02         0         1           Mybus 02         0         1           Mybus 04         0         1           Mybus 054         0         1           Mybus 066         0         0           Mybus 069         0         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RxTxEnable       |                        |              |                          |                   |         |                              | -               |

| Muse         Information         Information         Information         Information           B Musel         0         1         0         1         0         1           My bus 000         0         1         0         1         0         1           My bus 012         0         1         0         1         0         1           My bus 012         0         1         0         1         0         1           My bus 020         0         1         0         1         0         1           My bus 020         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Romata           | 0 0 1                  | وارول وار    | 1 .                      | 1,11              | յութի   | 10101 0 101                  | • • •           |

| θ- My bus 1         0   01 111 111 110 1000         01 110 1110 1110           - My bus 00         - 10 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Time             | -100 nst               | mimm         |                          |                   |         |                              | 2.26 us         |

| - Mrbus Op         0         1           - Mrbus Op         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | - My bus I       |                        |              | 010111111110             | 1000              | _χ      |                              | $ \rightarrow $ |

| - Mr bus QP - Mr b                                                                                                                                                                                                                                                                                                    | El Mybus Q       |                        |              | 1 00 0010 0001           | 0000              | =       | 1101 1010 1001 1011          |                 |

| Mrbus 002         0         1           Mrbus 001         0         1           Mrbus 004         1         0           Mrbus 005         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | My bus Q(0       |                        |              | 0                        |                   |         | t                            | Ĩ               |

| - Ma bus QQ2<br>- Ma bus QQ2<br>- Ma bus QQ4<br>- Ma bus QG6<br>- Ma bus QG6<br>- Ma bus QG6<br>- Ma bus QG7<br>- |                  |                        |              | n                        |                   |         |                              |                 |

| M bus QQ         0         1           -M bus QK         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                  |                        |              |                          |                   |         |                              |                 |

| Morbus Q(4 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  |                        |              | 0                        |                   |         |                              |                 |

| - My bus QP 0<br>- My b                    |                  |                        |              |                          | _                 |         |                              |                 |

| - Mybus 0)6 0<br>- Mybus 0)7 0 1<br>- Mybus 0)8 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                  |                        |              |                          |                   |         |                              |                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                  |                        | _            | -                        |                   |         |                              |                 |

| - My bus 0(8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -My bus Q(6      |                        |              | _                        | _                 | 0       |                              |                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -My bus Q(7      |                        |              | 0                        |                   |         |                              |                 |

| 4 5 4 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | My bus Q(8       |                        |              |                          |                   | 0       |                              | -               |

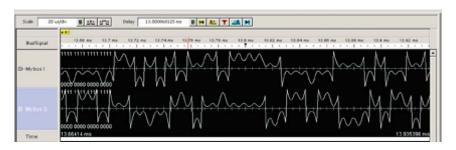

Figure 2. Agilent's logic analysis interface waveform view gives us a good picture of the relationships between the signals as well as a look at the waveforms themselves.

#### Introduction

Digital signals replacing analog

Digital signals are taking the place of analog in many areas. Traditionally, analog interfaces between RFICs and BBICs were standard. Now, chip manufacturers are producing chipsets with digital interfaces. Standards such as OBSAI and CPRI for base station chips and DigRF for mobile chips define a variety of digital interface possibilities. WiMedia defines a digital interface between the MAC and PHY chip. And it doesn't stop there – these types of digital interfaces are becoming common in software-defined radios (SDRs), satellite communications and radar systems, to name a few. This is a trend that is going to continue.

It makes sense – digital signals are easier and cheaper to implement and they will eventually enable better signal quality and lower power consumption. When such signals are implemented serially, they can also reduce the number of required IC pins, which saves chip makers money, and the saving typically is passed through to the end customer of consumer products.

The transition of analog to digital has not, however, changed the physical layer test requirements, and traditional analog test and measurement equipment is not suitable for digital RF design validation. Up until recently, this presented a problem. For example, how are we to make an EVM measurement off digital signals coming from an FPGA? The good news is that there is a way to do this using Agilent's logic analyzer tools with the 89601A vector signal analysis software, or the "digital VSA" as it's often called. Digital IQ signals from any logic device that can be connected to a logic analyzer can be measured in time, frequency and modulation domains.

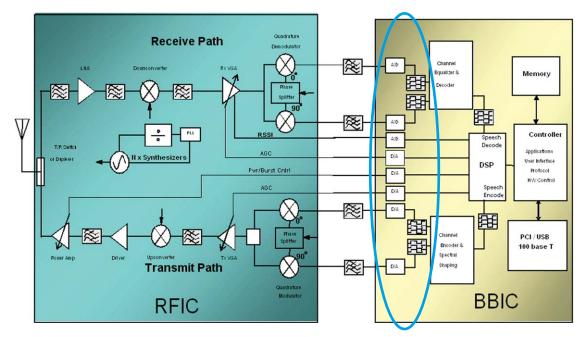

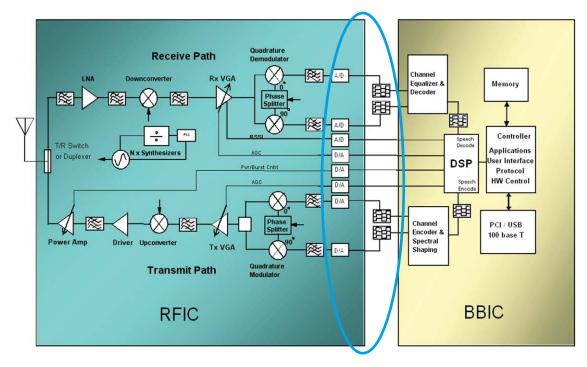

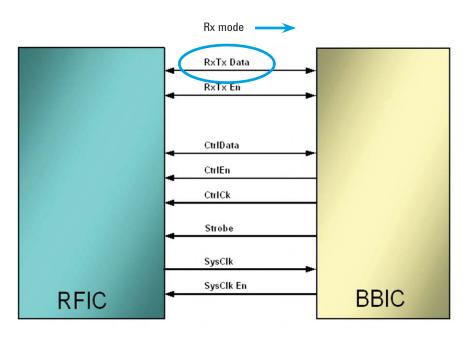

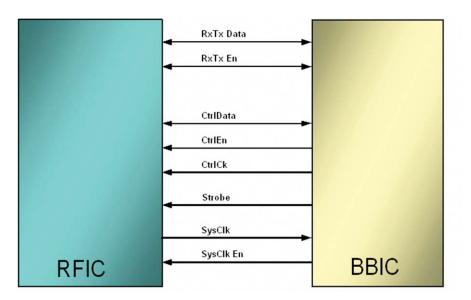

Interface changes

The transition from analog to digital interfaces does not involve a great deal of architectural change, but it does involve a move of the ADC/DAC circuitries from the RFIC to the BBIC. In some cases, the digital filtering is moved from the BBIC to the RFIC.

Serial or parallel?

Originally the digital interfaces were parallel – indeed, many still are. However, pin count on an IC is a precious resource. The average pin count for a digital parallel IQ interface is about 32 pins (not including the clocks) for a 16-bit I and 16-bit Q signal. Reduction of pin count is therefore a serious matter. Multiplexing turns out to be an easy way to implement the serial bit stream instead. This allows the signals to share common pins and greatly reduces pin count. Digital I and Q signals can be put into a serial format with some kind of time division multiplexing scheme. In some cases, as in DigRF Version 3, control data is multiplexed in, making measurements a little trickier.

The ADCs used to be located in the BBIC and the chip interface was analog.

Modern design has the ADCs placed in the RFIC, making the chip interface digital.

Figure 3. Changing interfaces

#### Logic analyzer basics

Many engineers entering the new world of digital signals are not very familiar with logic analyzers. Logic analyzers are not like spectrum analyzers or power meters or any of the standard analog test and measurement equipment. They are capable of performing very complex measurements on digital signals, and at first glance, they can look quite intimidating. The term "digital signals" refers to signals that take on a value of either 1 or 0, regardless of the type of logic (TTL, CMOS etc.) used. Logic analyzers are not as intimidating as they sometimes seem to new users at first glance. Once you become comfortable with the instrument, you'll realize that it's really quite easy to use.

The role of the logic analyzer:

A logic analyzer is a tool that gives you insight into the operation of a *digital* circuit by

- · Connecting to your DUT (device under test)

- · Capturing and storing the digital waveforms

- · Analyzing the stored data and displaying the results

With digital signals, the logic analyzer can:

- · Record a circuit's logic levels over time, and let you examine the record

- · Show whether or not a particular event happens (the trigger)

- · Provide a precise measure of time between events

- Inverse-assemble a microprocessor's logic levels to tell you what code was running

- Analyze complex buses and protocols

A logic analyzer is the perfect tool for connecting with the 89601A software for time, frequency and modulation domain measurements on digital IQ signals.

There are three steps to the logic analyzer process:

- Connect

- Acquire

- · Display data

Logic analyzer basics (continued)

#### **Connect:**

You have a few choices for connecting your logic analyzer to your DUT. First, there are general-purpose probes such as the flying lead probes. These probes have individual pin connectors. They are not always the best solution because sometimes there are signal integrity issues when you connect wire to wire, but they can be very handy when there is no other way to probe. They can also be used when it is necessary to get physically close to the DUT, as is the case in DigRF.

Another way to connect involves: building a "footprint" into the board ahead of time. It's fairly common to enable probing this way: think about digital debug ahead of time, plan for it, and design connectors into the board. This is no different from putting test points onto an RF board (SMAs or SMBs) that can be easily hooked up to a cable and spectrum analyzer. The footprint is a little bigger, but there are many digital signals instead of a single RF signal. A Samtec connector is an example of a solid connector that requires a footprint to be built into the board prior to fabrication.

Figure 4. Flying leads

Figure 5. Samtec connector

#### Acquire:

There are two measurement modes in logic analysis: timing and state. Timing analysis is for logic timing; it shows you when a logic event transitions. Timing analysis is asynchronous and uses the logic analyzer clock to determine when signal transitions occur relative to one another. With state analysis, we look primarily at events themselves: it shows where you would look for events that happened, as opposed to timing relationships. In state mode, the clock comes from the DUT. While we can certainly use timing mode to check signal transitions, when you use a logic analyzer with the 89601A software, we must using state mode. We are concerned with the bits (or samples as they are known in the logic analyzer world) and the order in which they appear.

#### **Display data:**

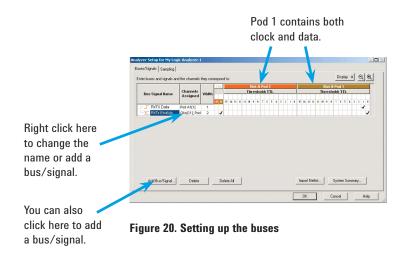

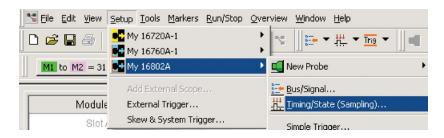

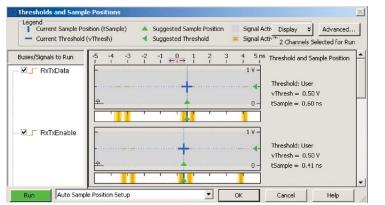

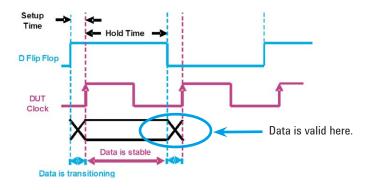

**Logic analyzer basics** (continued)