# 2 - 26.5 GHz GaAs MMIC Distributed Amplifier Conversion Guide

# Application Note # 47 - Rev. B

#### **1.0 Introduction**

Several electrical and physical characteristics of the HMMC-5021/22/26 family of 2-26.5 GHz distributed amplifiers have been modified. These changes were implemented to allow these devices to be fabricated using Hewlett-Packard's 3" GaAs production line. The fabrication mask and device layout has been changed slightly. However, the majority of physical and electrical characteristics of these devices has remained identical to those of the original components and these modifications should pose little or no impact on existing applications of these devices.

The characteristics affected by these modifications include:

- Physical topology.

- Typical DC and RF performance values.

- Out-of-band RF performance.

- Second gate bias circuitry and operation.

- Second gate absolute maximum voltage and current ratings.

Each of these modifications is described in the sections that follow.

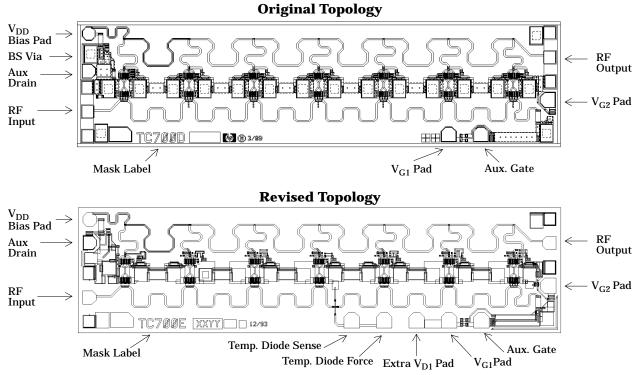

#### 2.0 Physical Topology

The overall appearance of the HMMC-5021/22/ 26 device has changed slightly. The new layout now shows the mask label as "TC700E" instead of "TC700D" to reflect the new mask used to fabricate the device. The auxiliary drain bonding pad which used to be located adjacent to a backside conductive via has been repositioned closer to the V<sub>DD</sub> bonding pad. The backside via has been eliminated. See Figure 1.

Also, three additional bonding pads have been

MWTC MARKETING May, 1995

HMMC-5021/22/26

added to the revised topology:

- An extra  $V_{G1}$  first gate bias pad, directly connected to the original pad, allows a second bond attempt should the first fail.

- Two new temperature diode sense and force pads which, when calibrated with an off-chip current source and voltage monitor, can be used to monitor the average chip temperature.

The location and function of all other RF and DC pads have not been altered. Connection to these new pads is not required for normal 2-26.5 GHz operation and therefore the topology changes should have no effect on existing applications.

#### 3.0 Typical DC and RF Performance Characteristics

The typical values for several DC and RF parameters have changed slightly to reflect the 50<sup>th</sup> percentile performance of the HMMC-5021/ 22/26 family of amplifiers fabricated with HP's 3" GaAs process. The changes are as follows:

#### • Nominal First Gate Control voltage (V<sub>G1</sub>) For Best Overall Performance

These amplifiers deliver the best overall gain, power and distortion performance when biased at  $V_{DD}$ =+7.0 volts, and  $I_{DD}$ =150 mA. The typical first gate control voltage range required to achieve this current has shifted more negative from the 0 to -0.4 volt range to the -0.2 to -0.5 volt range. In other words a slightly more negative first gate bias is required to operate the devices at 150 mA. The device may be operated at  $V_{G1}$ =0.0volts ( $I_{DD}$ = $I_{DSS}$ ) without exceeding acceptable reliability limits. However, the gain will be lower.

#### • Saturated Drain Current, (I<sub>DSS</sub>)

Typical  $I_{DSS}$  increased from 165 to 180 mA. The increase in this value is a direct result of process current targeting changes.

### • Pinch-Off Voltage, (V<sub>P</sub>)

Typical pinch-off voltage has been decreased from -1.3 volts to -1.5 volts also as a result of the change in process current targeting.

### • Second Gate, (V<sub>G2</sub>) Open-circuit Potential

The nominal second-gate open circuit potential has decreased from 2.4 volts to 2.1 volts due to a change in on-chip circuitry. (This circuitry change is described in more detail in a later section.)

### • First Gate Pinch-Off Current, (IDSOFF1)

The typical value has decreased from 6 to 4 mA. This change is due to the same topology change as described in the preceding section  $(V_{G2})$ .

# • Second Gate Pinch-Off Current, (I<sub>DSOFF2</sub>)

The typical value has decreased from 12 to 8 mA for the same reason as  $I_{DSOFF1}$ .

### • Small-Signal Gain, (S<sub>21</sub>)

The typical value has increased for each of the three specifications which makeup the

HMMC-5021/22/26 family of amplifiers. The gain increased from 8 to 10 dB for the HMMC-5021, from 9.5 to 10 dB for the HMMC-5022, and from 9.0 to 9.5 dB for the HMMC-5026.

#### • Gain Flatness ( $\Delta S_{21}$ )

The value, defined as  $\pm$ (max. gain - min. gain)/ 2, has decreased for each of the three specifications. The typical gain flatness decreased from  $\pm 1$  to  $\pm 0.5$  dB for the HMMC-5021, from  $\pm 0.8$ to  $\pm 0.5$  dB for the HMMC-5022, and from  $\pm 1$  to  $\pm 0.75$  dB for the HMMC-5026.

# • Output Power (P<sub>-1dB</sub>, P<sub>sat</sub>)

The typical output power values have been increased slightly for only the HMMC-5021 and -5022 amplifiers. This is a direct result of the higher current targeting for the new process. The power increased from 17.5 to 18 dBm ( $P_{-1dB}$ ) and from 19.5 to 20 dBm ( $P_{sat}$ ) for the HMMC-5021 and -5022 amplifiers.

# • Harmonic Distortion (H<sub>2</sub>)

One improvement realized from the migration of this family into the new process is the decrease in second harmonic distortion as a result of higher current targets and output powers as well as second-gate bias topology changes. The typical second harmonic value, in dBc, decreased from -23 to -25 dBc across all

Figure 1. HMMC-5021/22/26 Topology Changes

amplifiers in this family (@ Pout=+17 dBm).

#### 4.0 Out-of-band RF Performance Characteristics

The most significant change to the RF performance affects the "out-of-band" small- and largesignal performance of these amplifiers. Layout modifications were implemented to "roll-off" (i.e. decrease) the gain above 26.5 GHz and enhance the low temperature stability of the amplifiers. The gain, instead of staying relatively flat to 30 GHz, is now down by  $\approx$ 3 dB at 29.5 GHz. The gain at 26.5 GHz, while improved by ~ 0.5 dB over the original layout, now represents the point of lowest gain for all frequencies up to 26.5 GHz.

Layout modifications to the drain-line termination circuitry were implemented to improve the overall gain flatness of the amplifiers. The previous layout produced a maximum gain ( $S_{21max}$ ) occurring at 2 GHz. The new layout produces a maximum gain occurring around 6 GHz. For applications which use off-chip circuitry to extend the low-frequency operation of these devices below 2 GHz, the new layout will improve broadband flatness performance slightly.

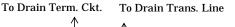

#### 5.0 Second Gate Bias Circuitry and Operation

On the original layout the second gate was selfbiased to between 2.4 and 2.6 volts by an on-chip resistive divider network. As a result the open circuit potential on  $V_{G2}$  was directly dependent on the drain bias applied to  $V_{DD}$  according to the following relation:

$$V_{G2} = 0.37(V_{DD})$$

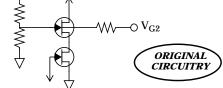

The newer topology incorporates two diodes in series with a small resistor connected between the second gate bias line and ground. This circuitry, in addition to a slight modification of the existing resistive divider (connecting the second gate bias line to the drain line), clamps the  $V_{G2}$  open circuit potential to  $\sim 2.1$  volts and improves low temperature stability. As a result the  $V_{G2}$  open-circuit potential is no longer a direct consequence of the  $V_{DD}$  bias voltage. The ability of the second gate to control the gain, current and power of the amplifier without affecting input or output return loss remains unaffected. See

Figure 2.

To Drain Term. Ckt. To Drain Trans. Line

Figure 2. HMMC-5021/22/26 V<sub>G2</sub> Circuitry Changes

#### 6.0 Second Gate Absolute Maximum Ratings

The maximum second gate voltage ( $V_{G2}$ ) has been decreased from +5 volts to +3.5 volts. Since the maximum gain is achieved when the second gate is set at its open-circuit floating potential (~ 2.1 volts), any forced value greater than this voltage does not increase the gain. The maximum voltage has been decreased to account for the drop in maximum allowable voltage the new second gate on-chip circuitry will tolerate.

The minimum second-gate current has been increased from -20 to -7 mA to reflect the resulting current which exists when the device is operated at minimum second-gate voltage (-2.5 volts).

For additional information refer to Application note #34, *HMMC-5021/22/26/27 Users Guide*, or contact Gordon DeWitte at (707) 577-3887, or Mark Thorn at (707) 577-4540.