# ELECTRONIC COUNTER 5345A

# CERTIFICATION

Hewlett-Packard Company certifies that this instrument met its published specifications at the time of shipment from the factory. Hewlett-Packard Company further certifies that its calibration measurements are traceable to the United States National Bureau of Standards, to the extent allowed by the Bureau's calibration facility, and to the calibration facilities of other International Standards Organization members.

# **WARRANTY AND ASSISTANCE**

This Hewlett-Packard product is warranted against defects in materials and workmanship for a period of one year from the date of shipment. Hewlett-Packard will, at its option, repair or replace products which prove to be defective during the warranty period provided they are returned to Hewlett-Packard, and provided the preventive maintenance procedures in this manual are followed. Repairs necessitated by misuse of the product are not covered by this warranty. NO OTHER WARRANTIES ARE EXPRESSED OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. HEWLETT-PACKARD IS NOT LIABLE FOR CONSEQUENTIAL DAMAGES.

Service contracts or customer assistance agreements are available for Hewlett-Packard products.

For any assistance, contact your nearest Hewlett-Packard Sales and Service Office. Addresses are provided at the back of this manual.

# 5345A ELECTRONIC COUNTER

OPERATING AND SERVICE MANUAL

# **SERIAL PREFIX: 1708A**

This manual applies directly to HP Model 5345A Electronic Counters having serial number prefix 1708A.

# **NEWER INSTRUMENTS**

This manual, with enclosed "Manual Changes" sheet, applies to HP Model 5345A Electronic Counters having serial number prefixes as listed on the "Manual Changes" sheet.

# **OLDER INSTRUMENTS**

For serial prefixes below 1708A; refer to Section VII

MANUAL PART NUMBER 05345-90026 Microfiche Part Number 06345-90026 PRINTED IN U.S.A. Printed: FEB. 1977

HEWLETT-PACKARD COMPANY 1974

# **TABLE OF CONTENTS**

# **GENERAL**

**Specifications**

# INSTALLATION

Initial Set Up, Remote Programming

# **OPERATION**

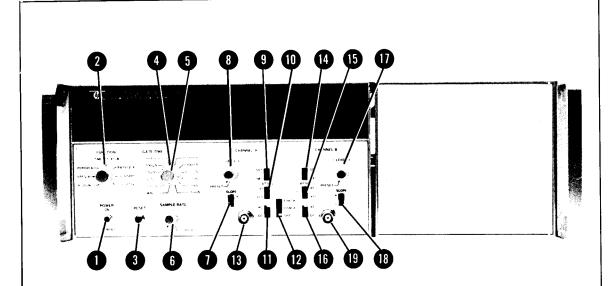

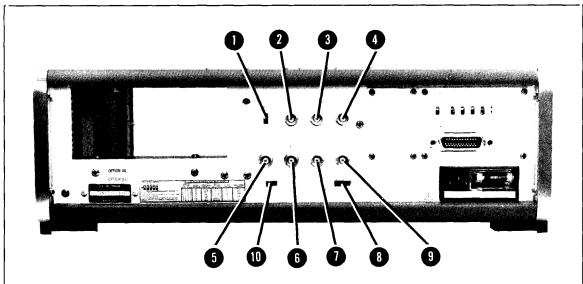

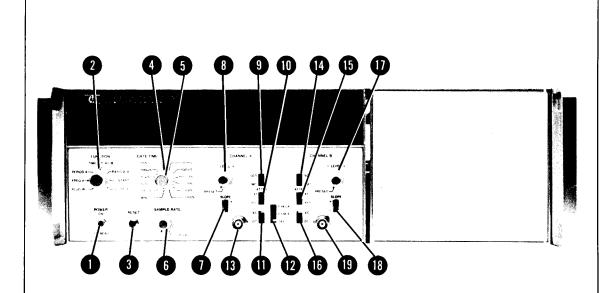

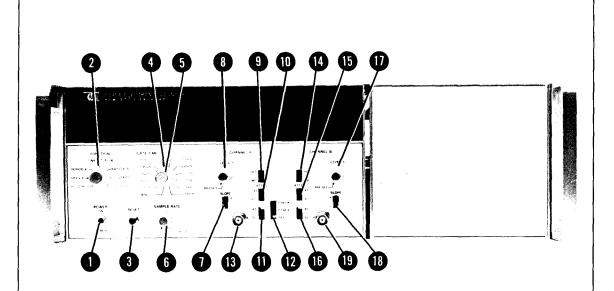

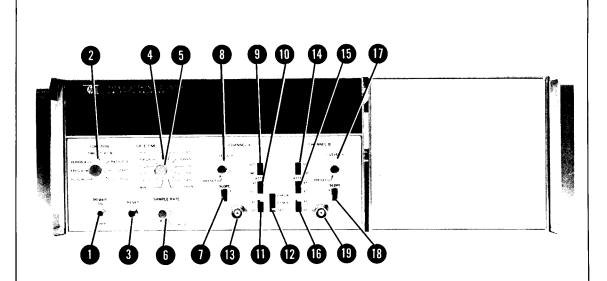

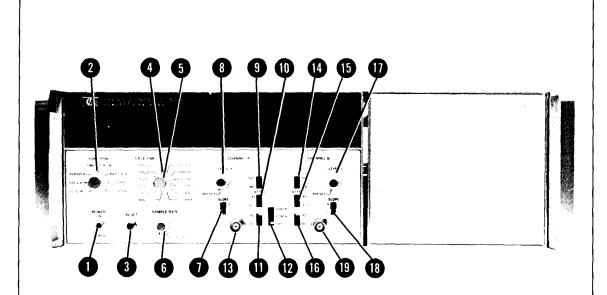

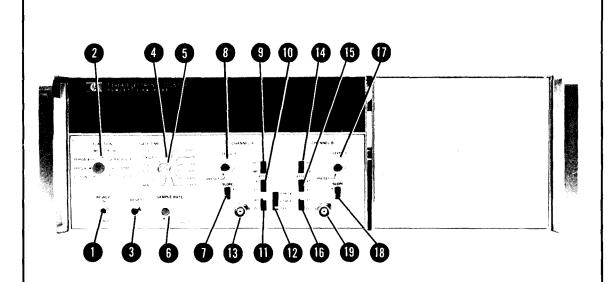

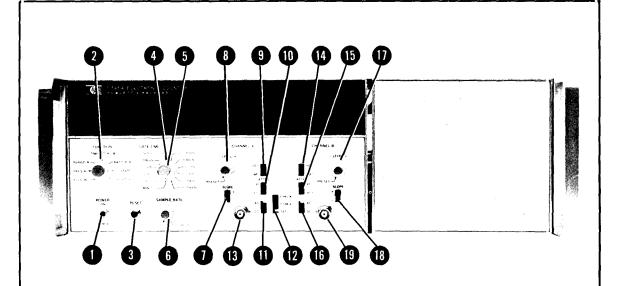

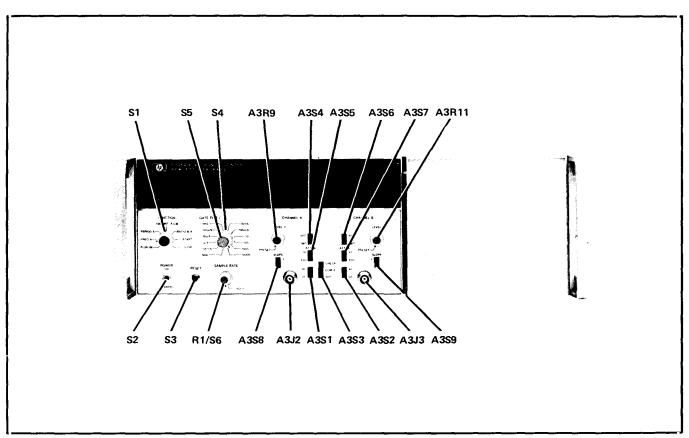

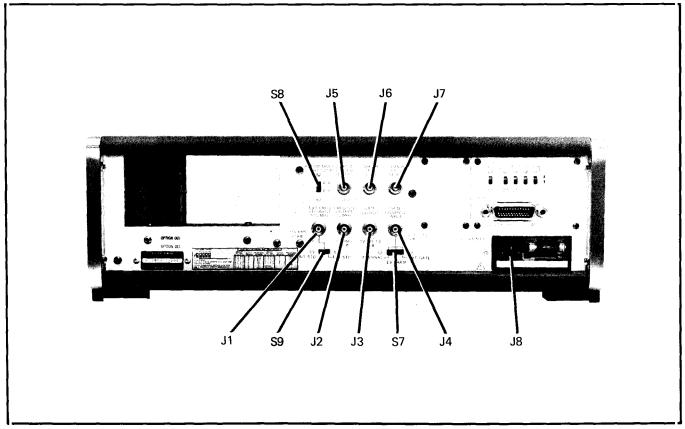

Front and Rear Panel Controls and Connectors

# THEORY

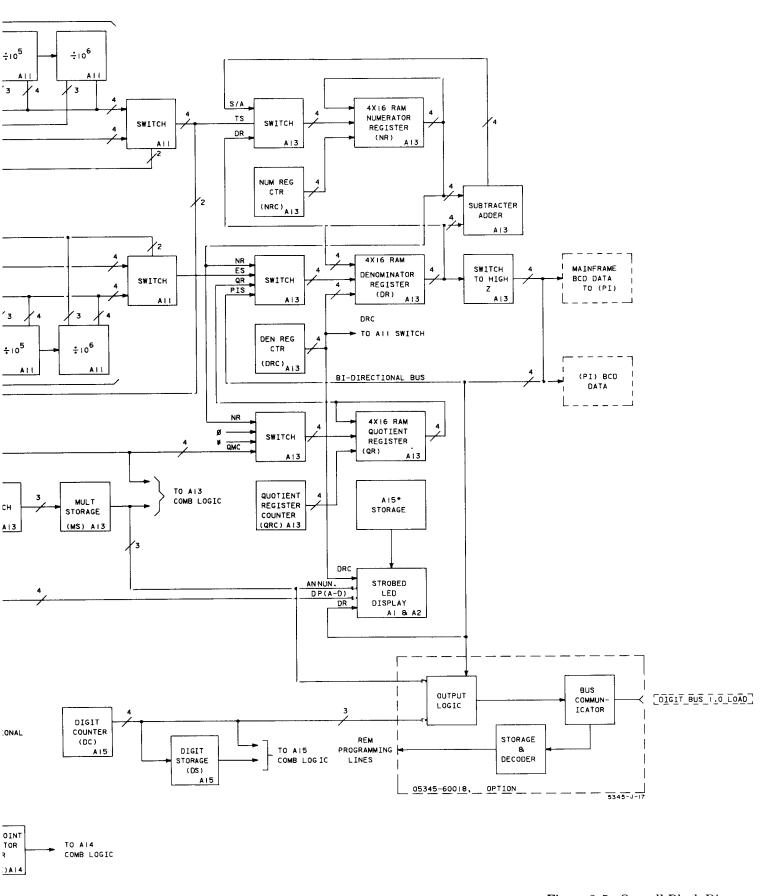

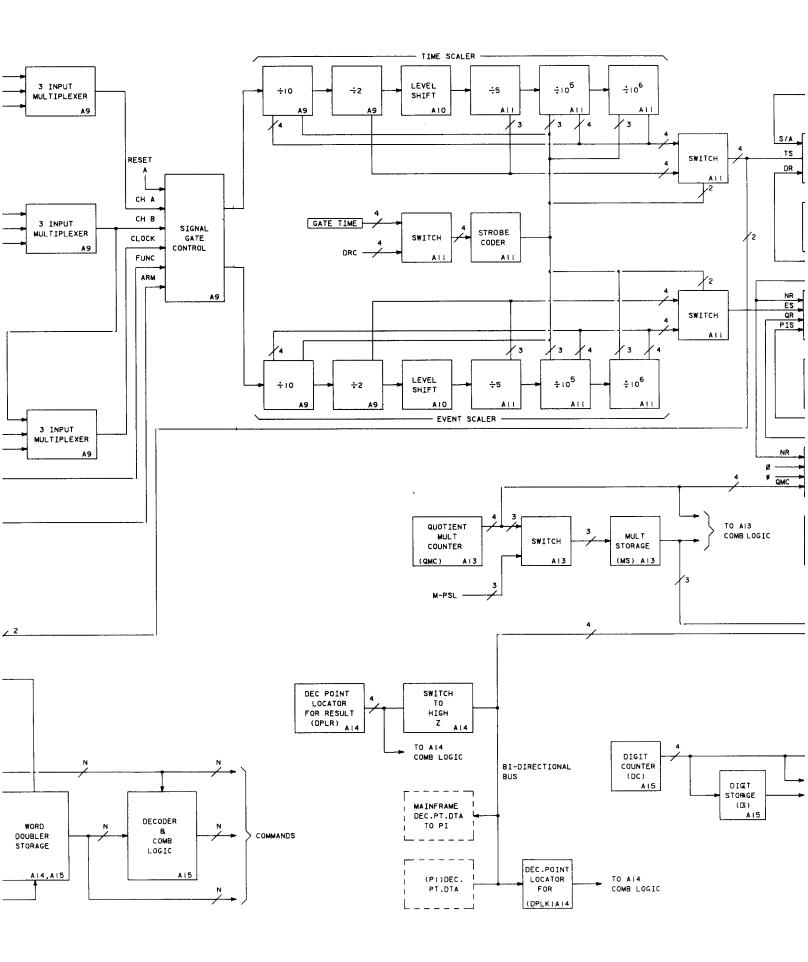

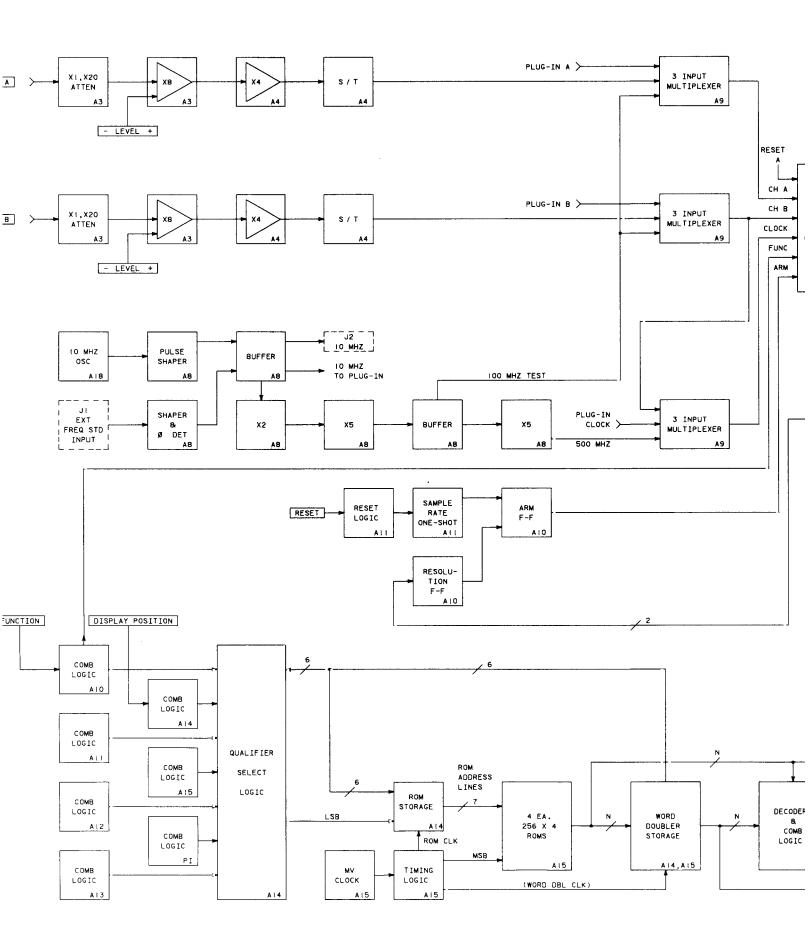

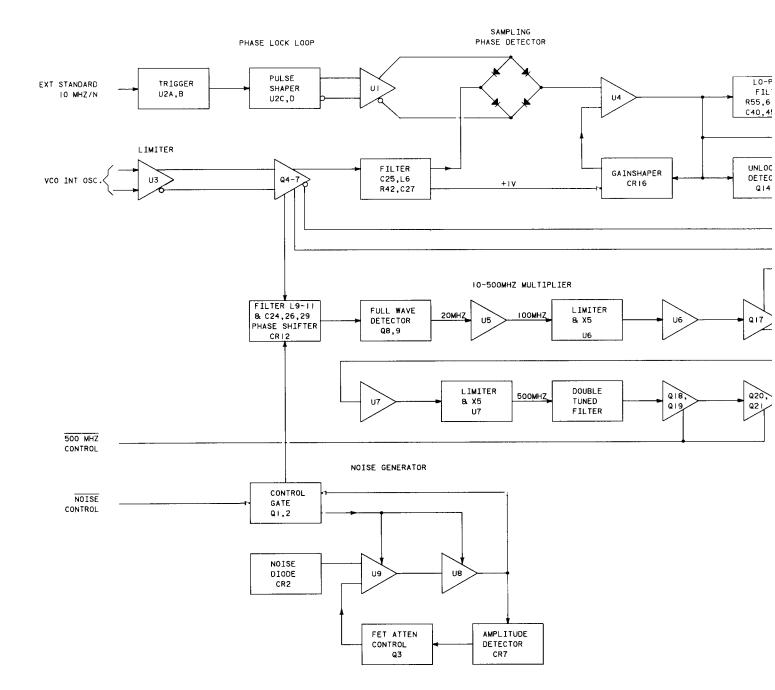

Block Diagram Theory, Circuit Theory, I.C. Theory

# MAINTENANCE

Troubleshooting, Adjustments, Specification Verification

**REPLACEABLE PARTS**

# MANUAL CHANGES AND OPTIONS

Option Description and Installation, Manual Backdating

# **CIRCUIT DIAGRAMS**

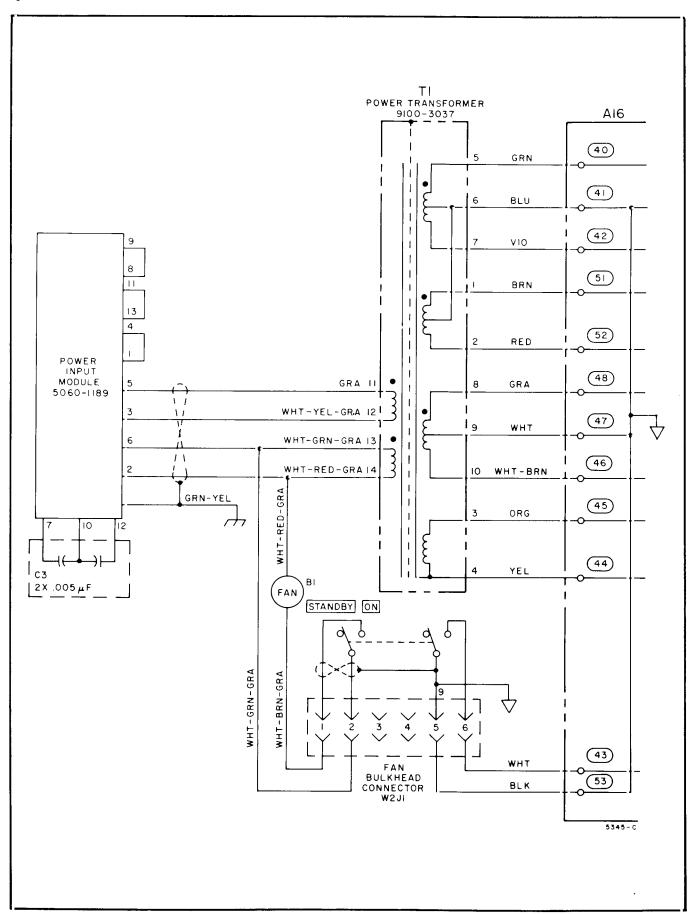

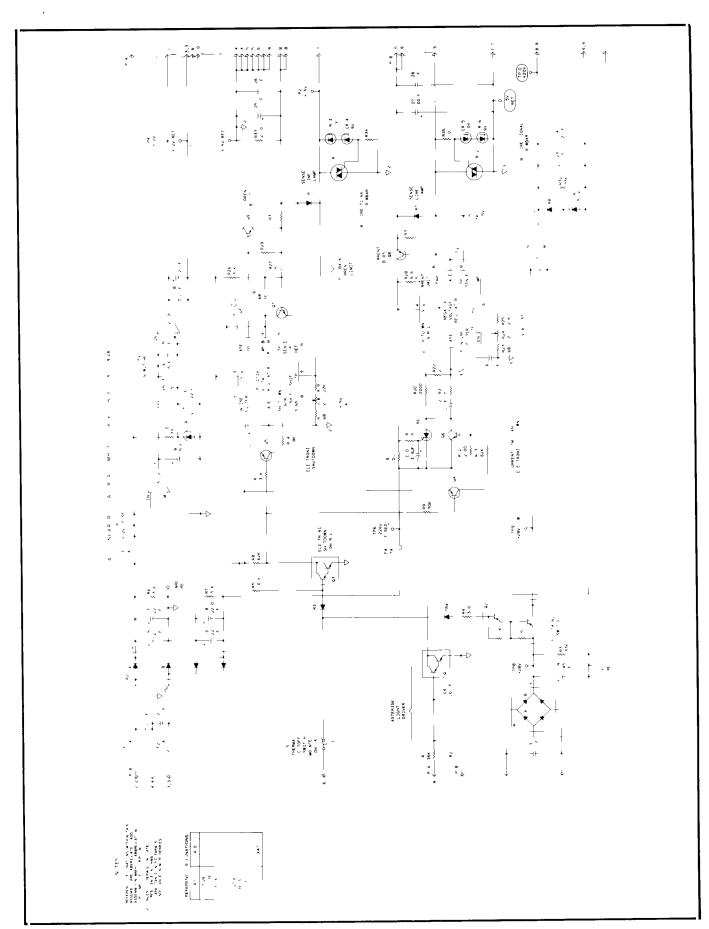

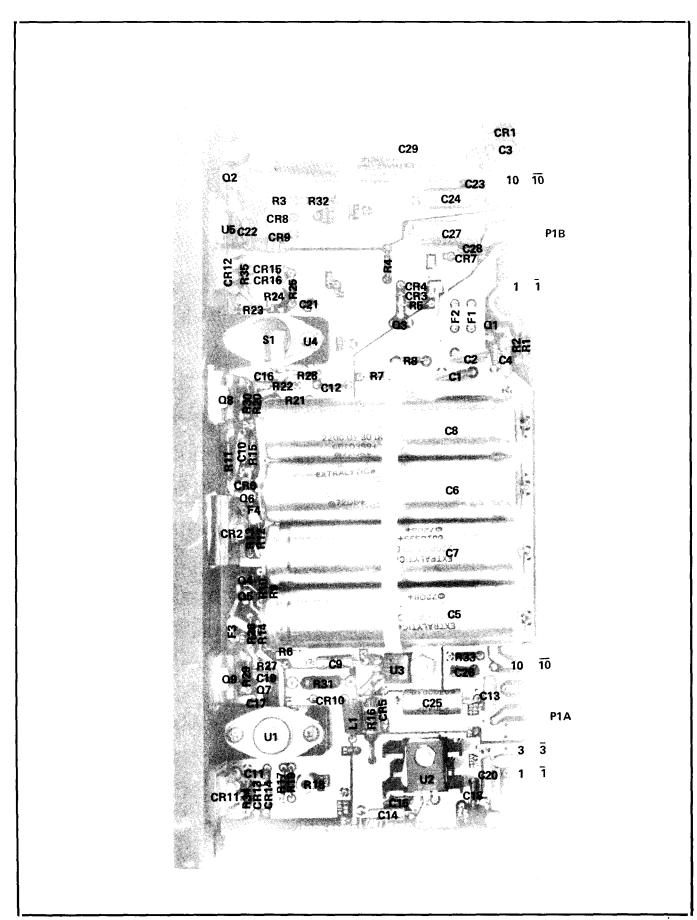

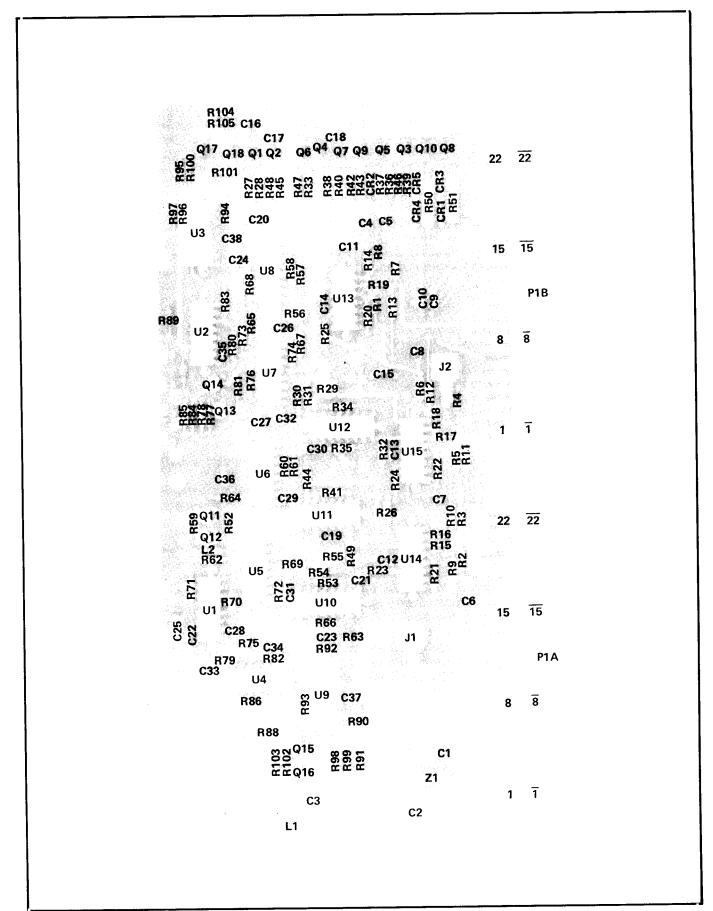

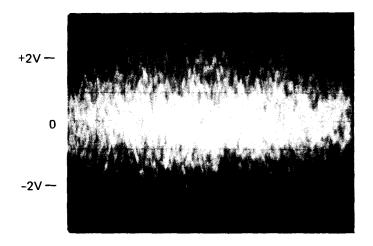

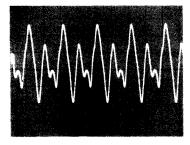

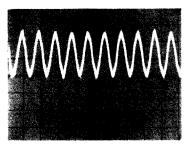

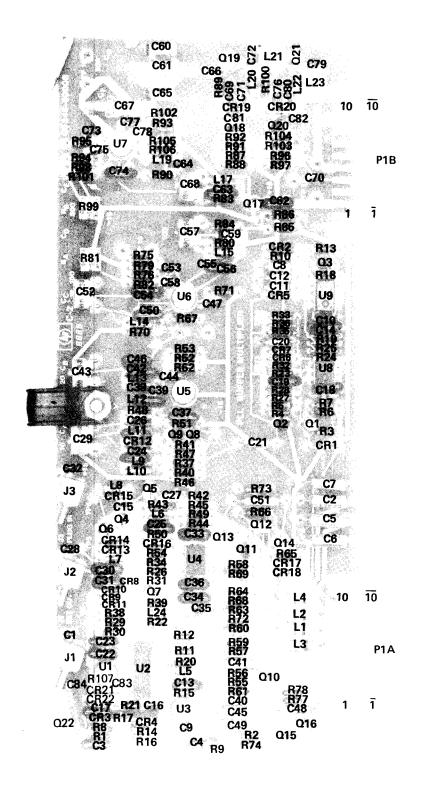

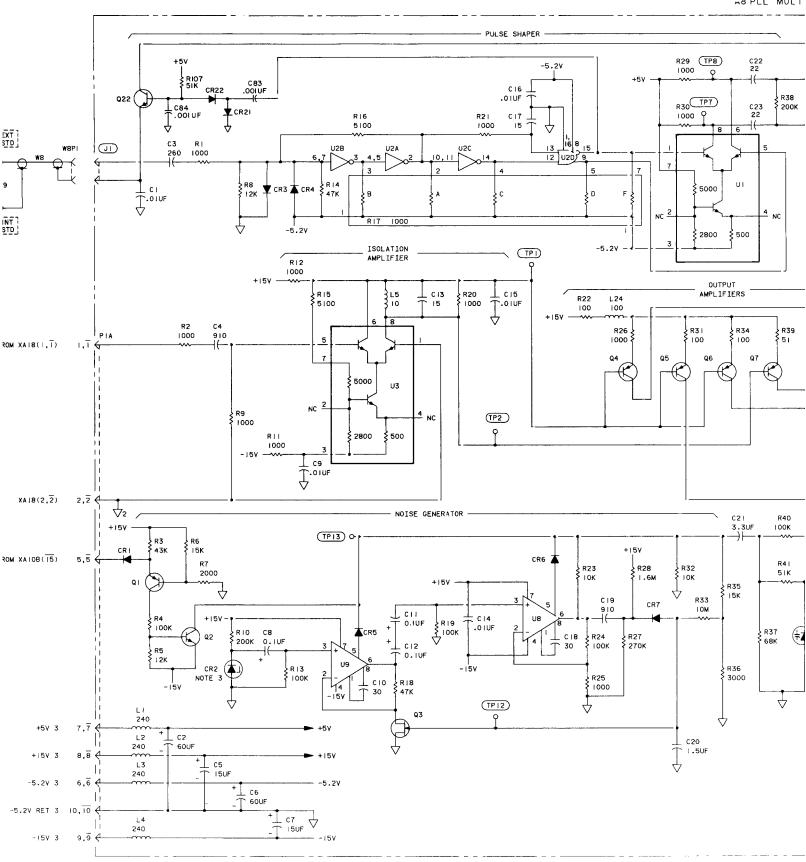

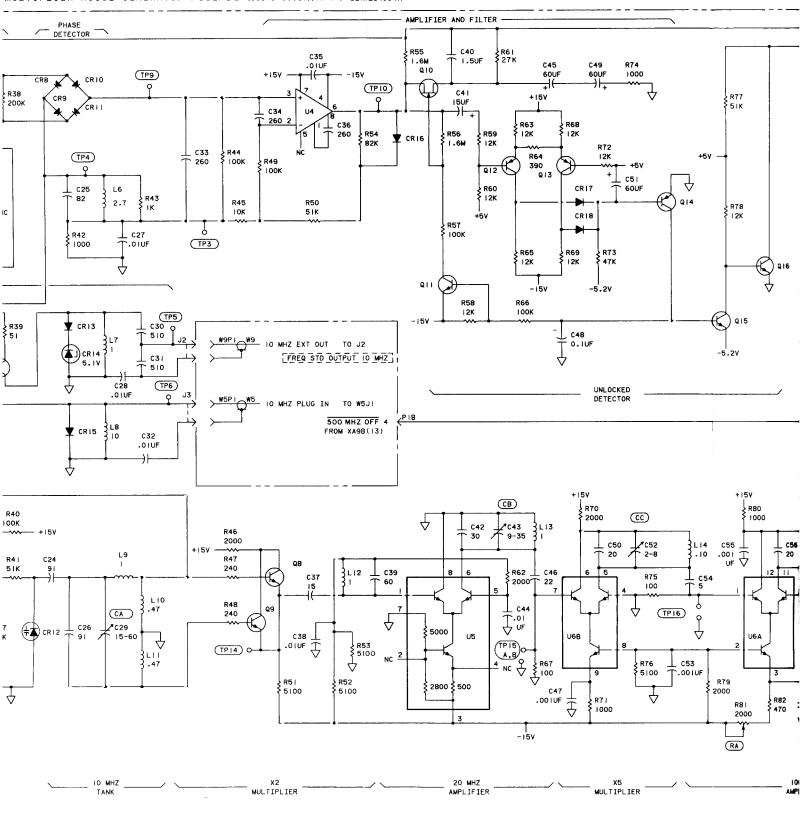

Schematics, Component Locators, Waveforms, Block Diagrams

# **TABLE OF CONTENTS**

| Section                |              |                                                          | Page |

|------------------------|--------------|----------------------------------------------------------|------|

| I                      | GENE         | ERAL INFORMATION                                         | 1-1  |

|                        | 1-1.         | Description                                              | 1-1  |

|                        | 1-4.         | Instrument Identification                                | 1-1  |

|                        | 1-6.         | Options                                                  | 1-1  |

|                        | 1-8.         | Accessories                                              | 1-1  |

| II                     | INST         | ALLATION AND REMOTE PROGRAMMING                          | 2-1  |

|                        | 2-1.         | Introduction                                             | 2-1  |

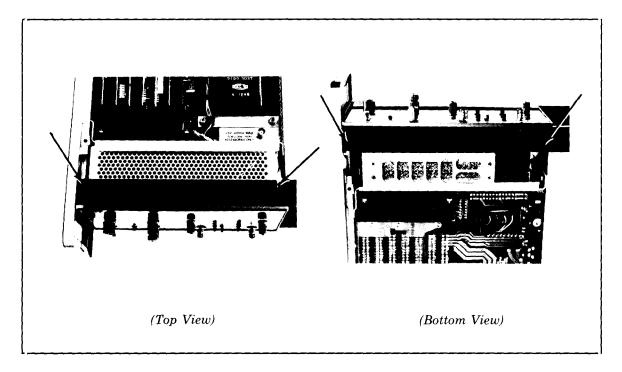

|                        | 2-3.         | Unpacking and Inspection                                 | 2-1  |

|                        | <b>2–</b> 5. | Installation Requirements                                | 2-1  |

|                        | 2-9.         | Repacking for Shipment                                   | 2-2  |

|                        | 2-11.        | Environment During Storage and Shipment                  | 2-2  |

| ,                      | 2-13.        | Remote Programming and Digital Output (Options 010, 011) | 2-2  |

|                        | 2-15.        | Bus Description                                          | 2-2  |

|                        | 2-20.        | Data Transfer                                            | 2-7  |

|                        | 2-23.        | What Can Be Programmed                                   | 2-7  |

|                        | 2-25.        | Output Format                                            | 2-7  |

|                        | 2-27.        | Addressing the 5345A                                     | 2-7  |

|                        | 2-32.        | Computer Dump                                            | 2-8  |

|                        | 2-35.        | Computer Dump Format                                     | 2-8  |

|                        | 2-39.        | Computer Dump Programming                                | 2-9  |

|                        | 2-41.        | Line Characteristics                                     | 2-10 |

|                        | 2-43.        | Hardware                                                 | 2-10 |

|                        | 2-47.        | Programming the 5345A (Option 011 Only)                  | 2-13 |

|                        | 2-50.        | Program Function Descriptions (Option 011 Only)          |      |

|                        | 2-50a.       |                                                          |      |

|                        | 2-51.        | Output Process                                           |      |

|                        | 2-54.        | Modes of Operation (Option 011 Only)                     |      |

|                        | 2-57.        | Starting a Measurement Procedure (Option 011 Only)       |      |

|                        | 2-59.        | Examples of Programming (Option 011 Only)                | 2-19 |

|                        | 2-66.        | Option 012 Factory Installed Remote Programming          | 2-22 |

|                        | 2-69.        | Postures                                                 | 2-22 |

|                        | 2-71.        | Special Programming Considerations (Not in Option 011)   | 2-22 |

|                        | 2-73.        | 5845A Option 011 with 9820A/21A Calculator               |      |

|                        |              | Programming Summary                                      | 2-23 |

|                        | 2-74.        | 5345A Implementation of Bus Features                     | 2-25 |

|                        | 2-75.        | 5345A Typical Output Speed                               | 2-26 |

| III                    | OPER         | ATION                                                    | 3-1  |

|                        | 3-1.         | Introduction                                             | 3-1  |

|                        | 3-3.         | Measurement Technique                                    | 3-1  |

|                        | 3-5.         | Operating Modes                                          | 3-1  |

|                        | 3-7.         | Frequency Mode                                           | 3-1  |

|                        | 3-10.        | Period Modes                                             | 3-1  |

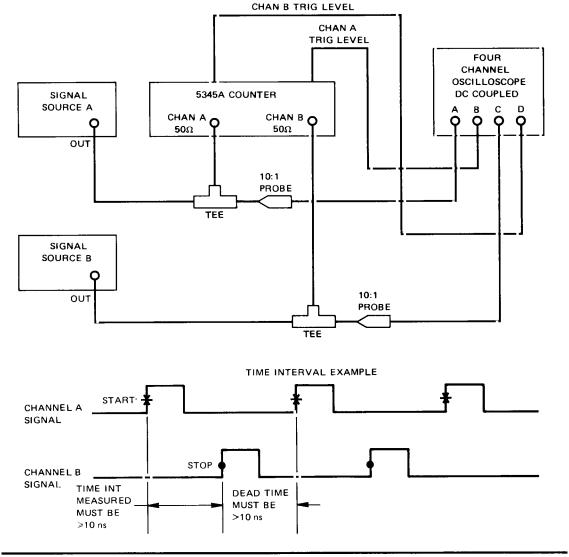

|                        | 3-15.        | Time Interval Modes                                      | 3-2  |

|                        | 3-24.        | Ratio Measurements                                       | 3-3  |

|                        | 3-29.        | Totalize Mode                                            | 3-4  |

| i i                    | 3-34.        | Input Triggering                                         | 3-4  |

|                        | 3-36.        | Excessive Gate Time                                      | 3-5  |

|                        | 3-38.        | External Arming and Gating                               | 3-5  |

|                        | 3-40.        | External Arming                                          | 3-5  |

| , or<br>1, or<br>1, or | 3-42.        | External Gating                                          |      |

|                        | 3-47.        | Time Interval Measurements                               | 3-6  |

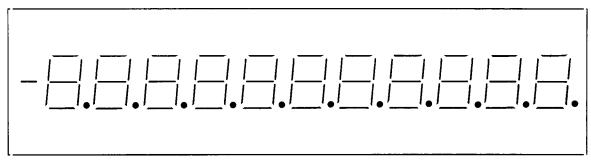

|                        | 3-51.        | Display                                                  | 3-8- |

| \$<br>\$               | 3-53.        | Display Position                                         | 3-8  |

| į                      | 3-55.        | Asterisk                                                 | 3-8  |

| - 2-<br>               | 3-50.        | Arm light                                                |      |

# TABLE OF CONTENTS (Continued)

| Section            |                    |                                                                                                                      | Page       |

|--------------------|--------------------|----------------------------------------------------------------------------------------------------------------------|------------|

| WHI                | OPER               | ATION (Cont'd)                                                                                                       |            |

| *** <del>***</del> | 3-61.              | Gate Light                                                                                                           | 3-8        |

|                    | 3-63.              | Lamp Test                                                                                                            |            |

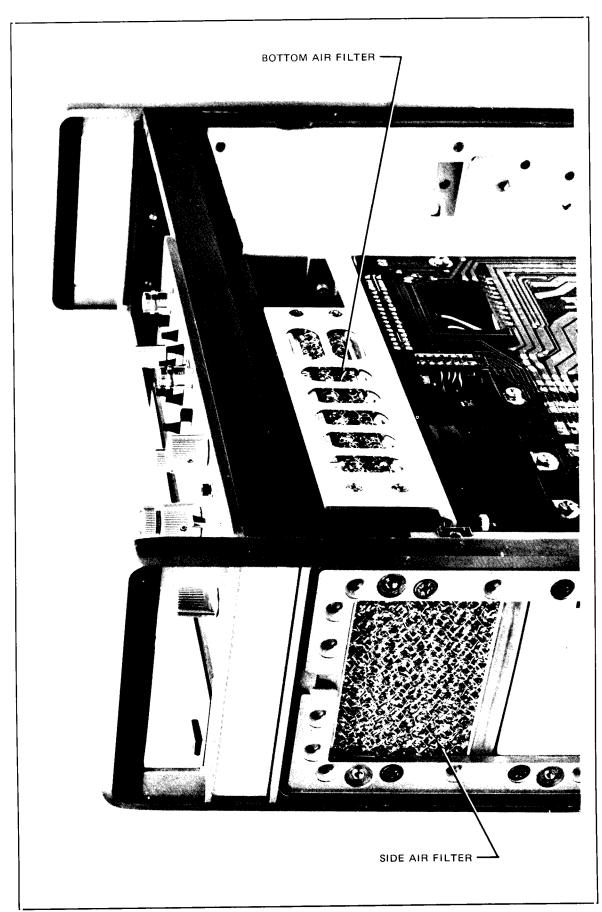

|                    | 3-66.              | Cooling                                                                                                              |            |

|                    | 3-68.              | Air Filter Cleaning                                                                                                  |            |

|                    |                    |                                                                                                                      |            |

| IV                 | THEC               | DRY OF OPERATION                                                                                                     | 4-1        |

|                    | 4-1.               | Introduction                                                                                                         | 4-1        |

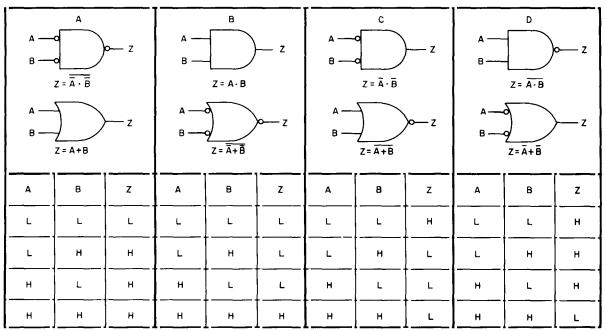

|                    | 4-3.               | Logic Elements                                                                                                       |            |

|                    | 4-5.               | Logic Levels                                                                                                         |            |

|                    | 4-7.               | Wire-OR/Wire-AND Configuration                                                                                       |            |

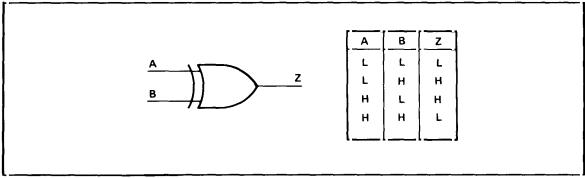

|                    | 4-10.              | Exclusive OR Gate                                                                                                    | 4-2        |

|                    | 4-12.              | Integrated Circuits — Theory of Operation                                                                            |            |

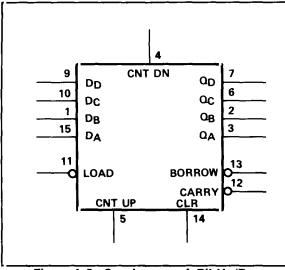

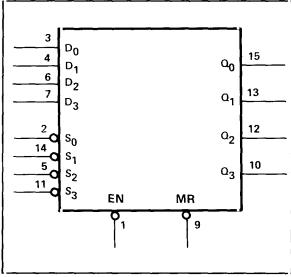

|                    | 4-14.<br>4-16.     | Synchronous 4-Bit Up/Down Counter, 1820-0233                                                                         | 4-2<br>4-3 |

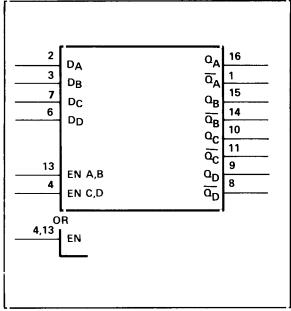

|                    | 4-10.<br>4-18.     | 4-Bit Bistable Latch, 1820-0301                                                                                      |            |

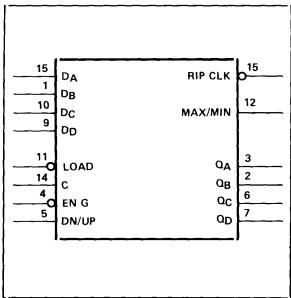

|                    | 4-20.              | Synchronous Up/Down Counter, 1820-0545                                                                               |            |

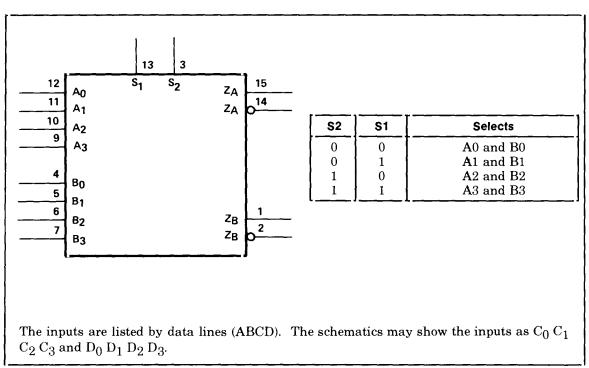

|                    | 4-22               | Dual Four-Input Multiplexer, 1820-0610                                                                               |            |

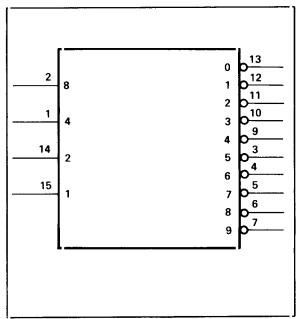

|                    | 4-24.              | One-of-Ten Decoder, 1820-0627                                                                                        |            |

|                    | 4-26.              | MOS Six Decade Counter, 1820-0634                                                                                    |            |

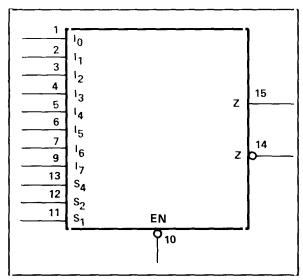

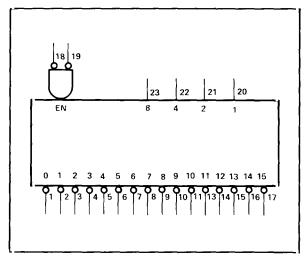

|                    | 4-28.              | Eight-Input Multiplexer, 1820-0658                                                                                   | 4-6        |

|                    | 4-30.              | Quad Latch, 1820-0701                                                                                                |            |

|                    | 4-32.              | One-of-Sixteen Deceder, 1820-0702                                                                                    | 4-6        |

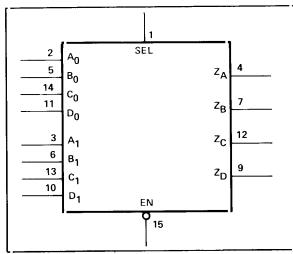

|                    | 4-34.              | Quad Two-Input Multiplexer, 1820-0710                                                                                | 4-7        |

|                    | 4-36.              | Synchronous 4-Bit Counter, 1820-0716                                                                                 | 4-7        |

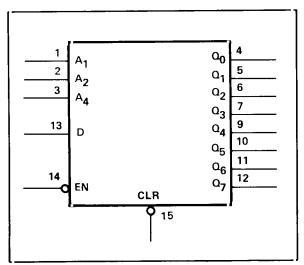

|                    | 4-38.              | 8-Bit Addressable Latch, 1820-0833                                                                                   | 4-7        |

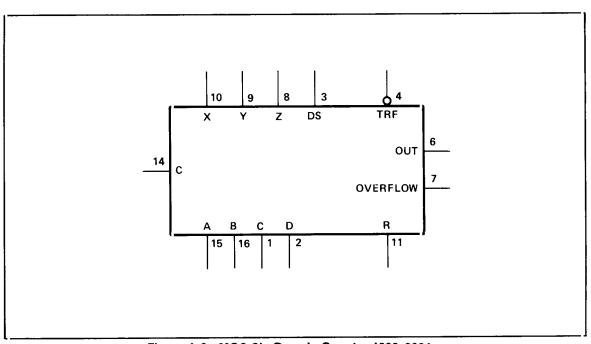

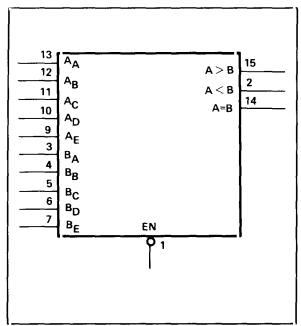

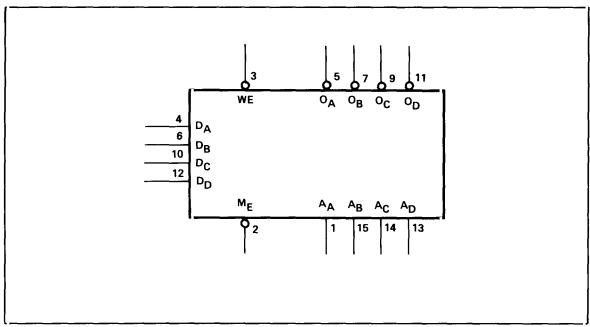

|                    | 4-40.              | 5-Bit Comparator, 1820-0904<br>64-Bit Read/Write Memory, 1820-1028                                                   | 4-8        |

|                    | 4-42.<br>4-44.     | Overall Theory of Operation                                                                                          | 4-8<br>4-9 |

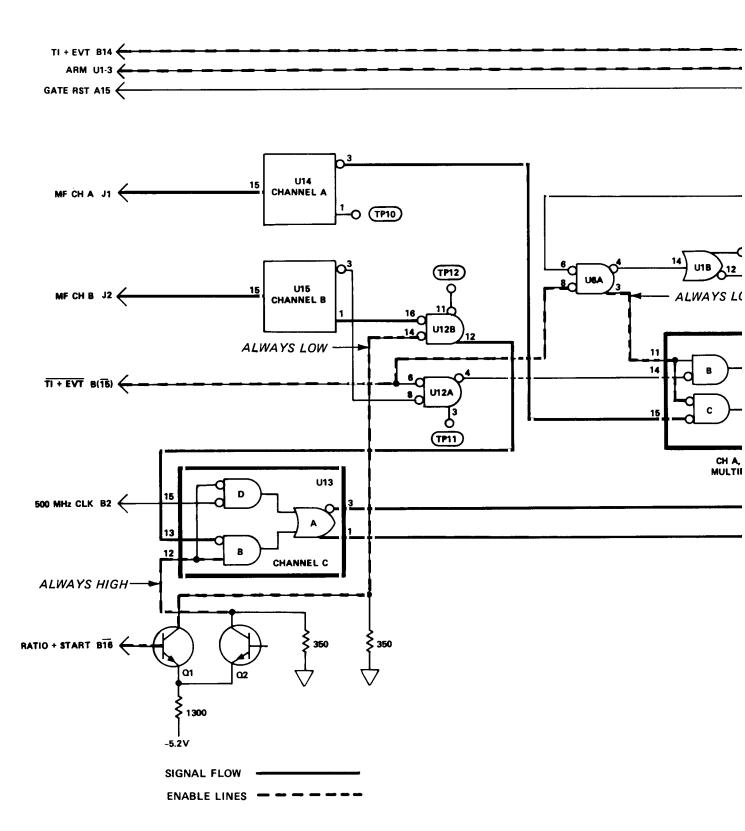

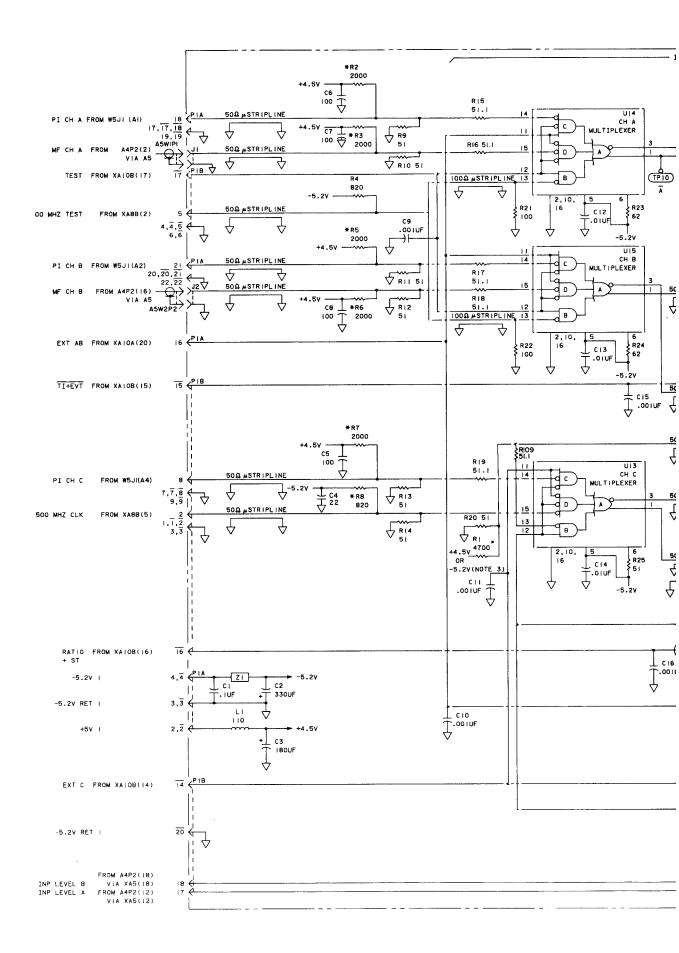

|                    | 4-46.              | Input Assembly                                                                                                       |            |

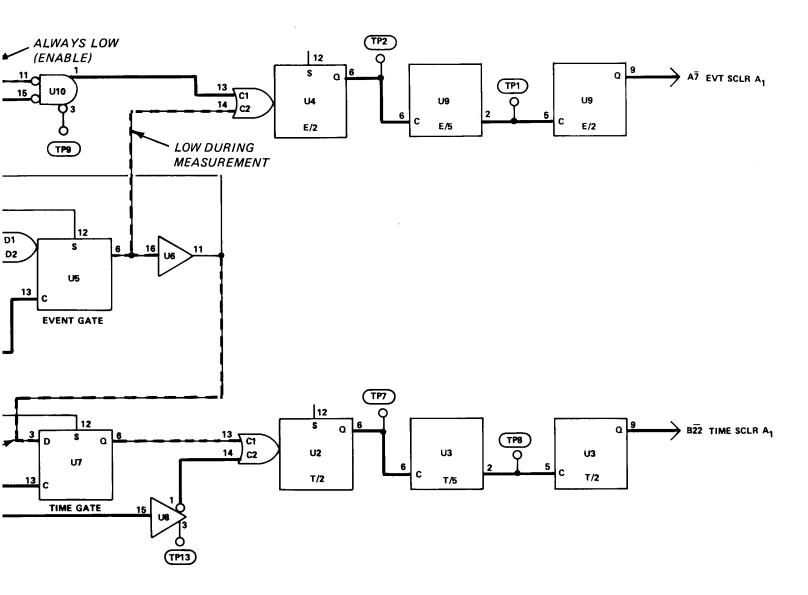

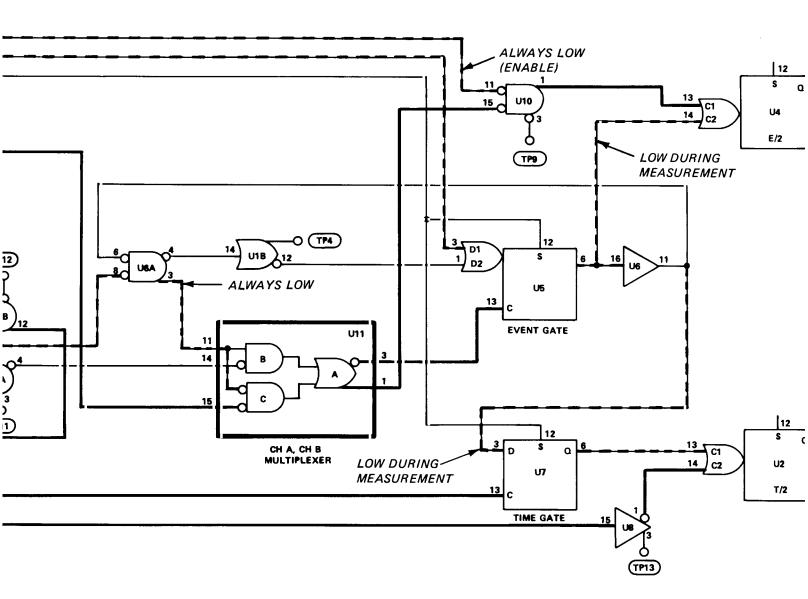

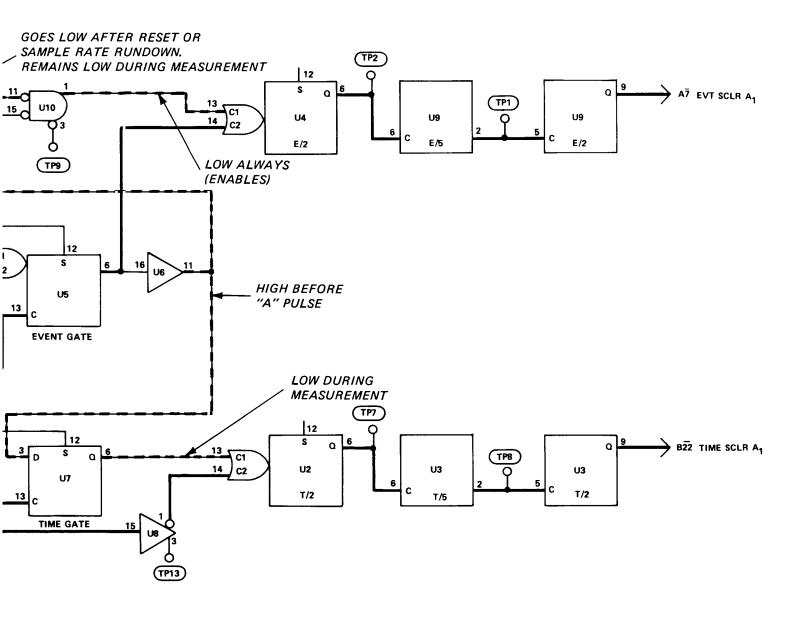

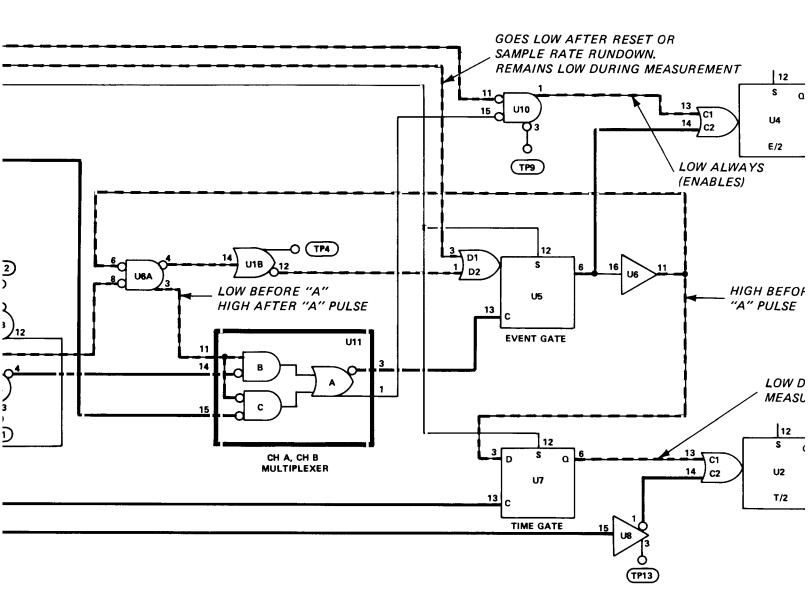

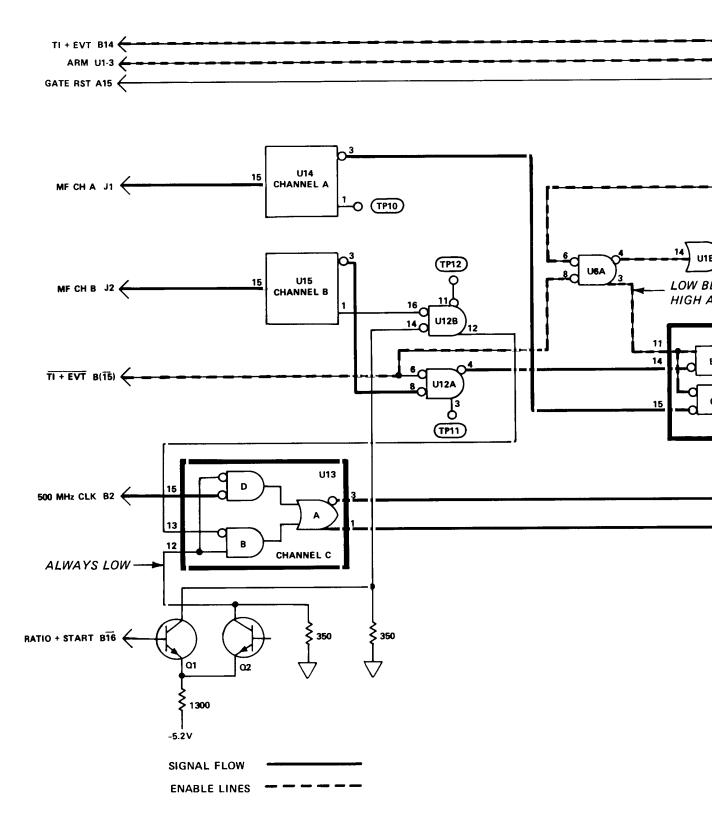

|                    | 4-48.              | Gate                                                                                                                 |            |

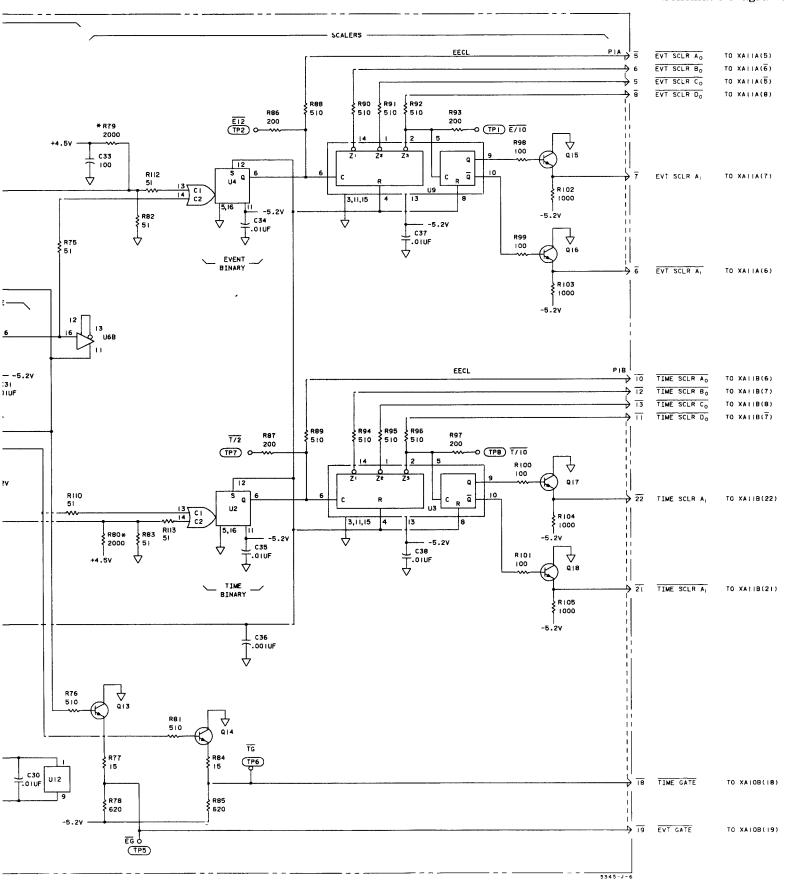

|                    | 4-51.              | Scattere                                                                                                             | 4-9        |

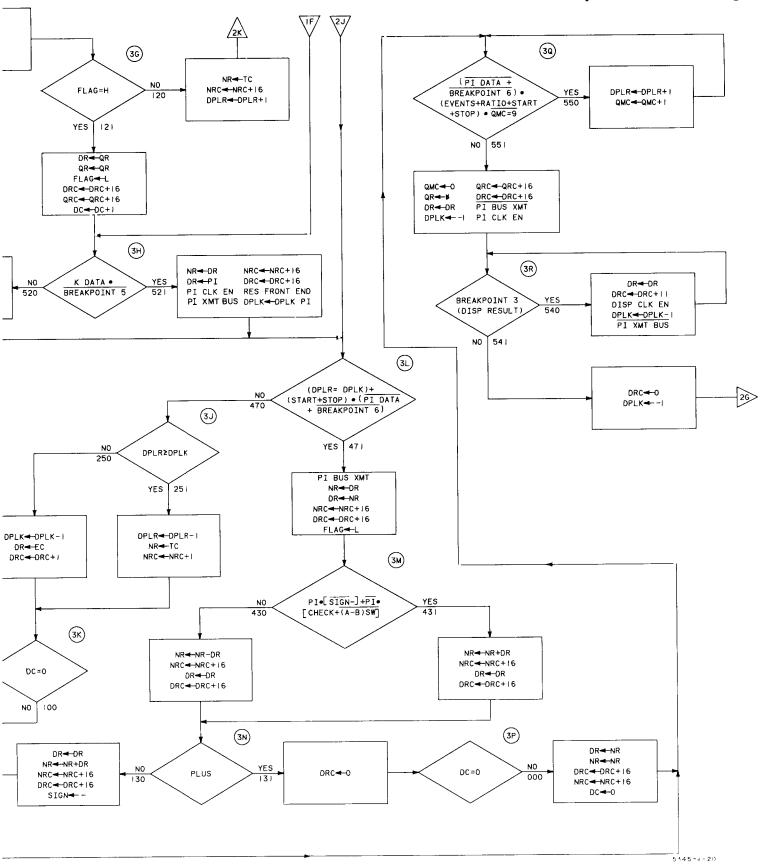

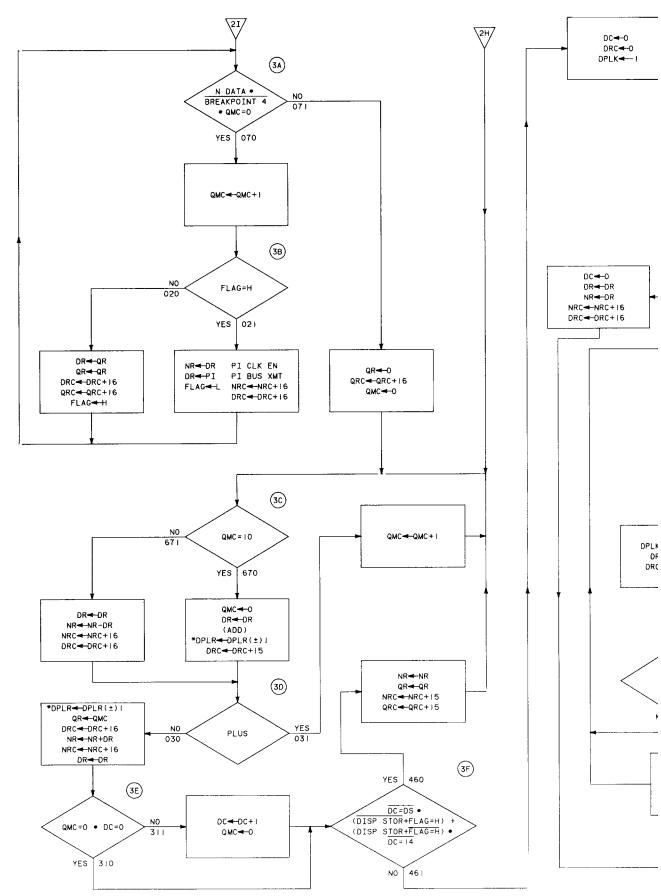

|                    | 4-55.              | Arithmetic Processor                                                                                                 | 4-9        |

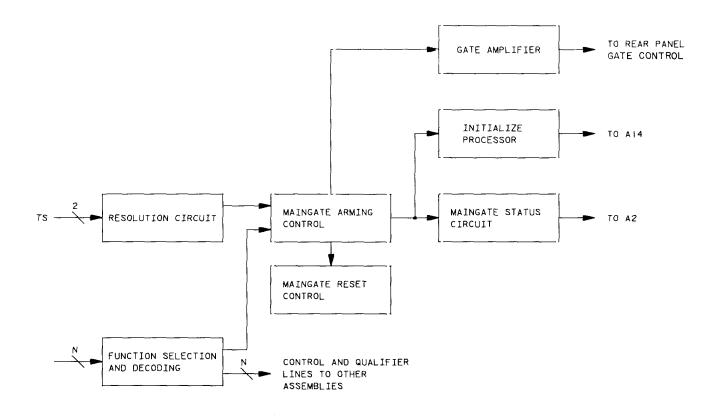

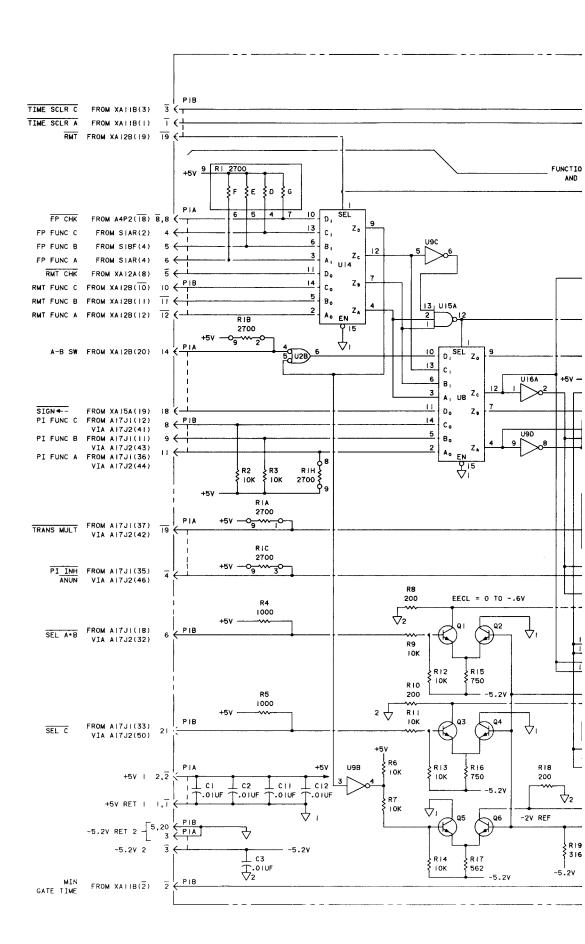

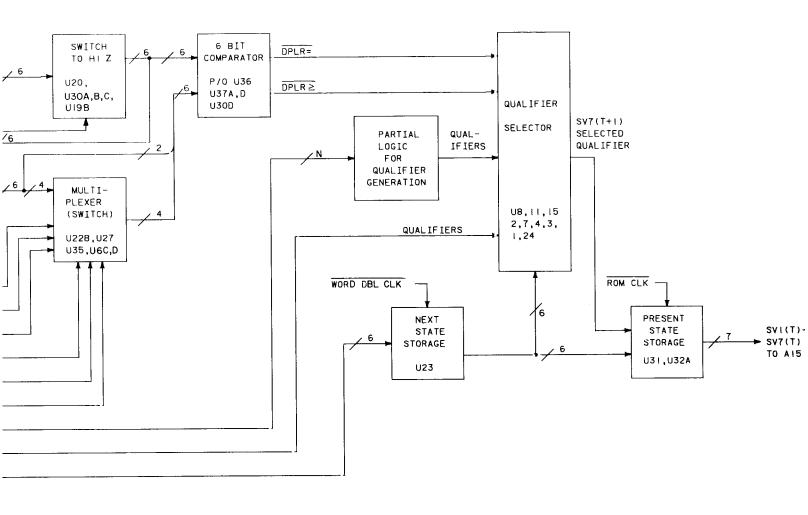

|                    | 4-61.              | State Control Section                                                                                                | 4-10       |

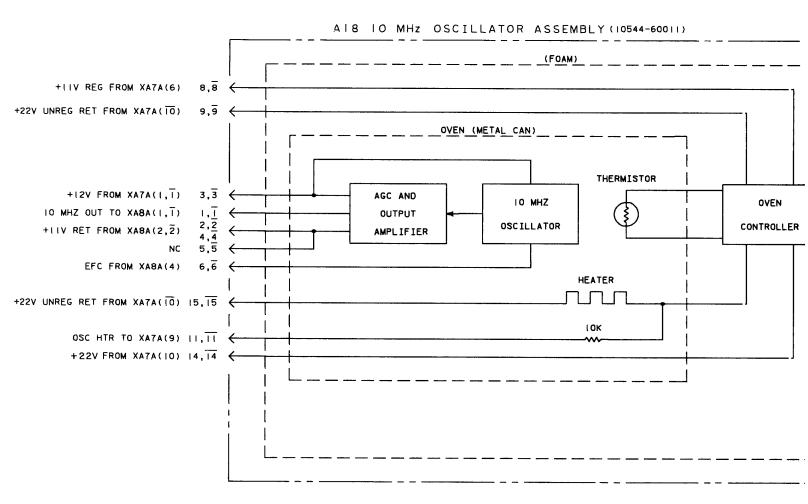

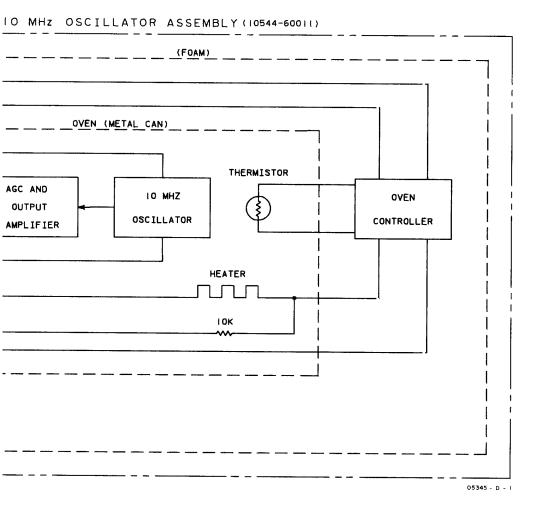

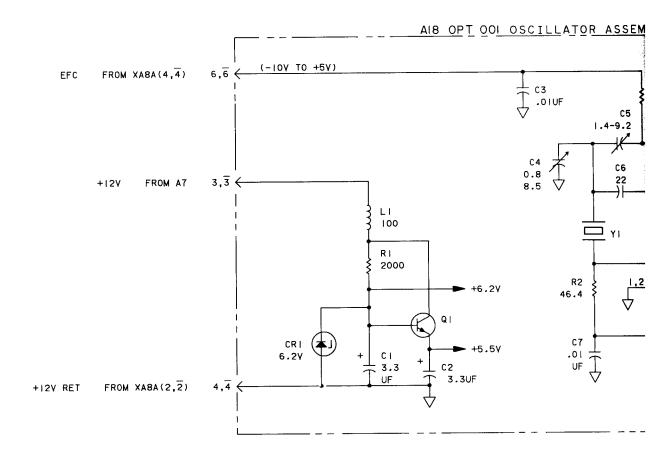

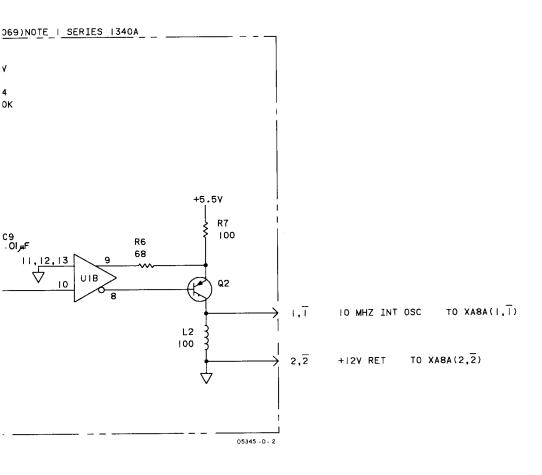

|                    | 4-66.              | Oscillator Circuits                                                                                                  | 4-11       |

|                    | 4-69.              | Power Supplies                                                                                                       | 4-11       |

|                    | 4-71.              | Circuit Board Theory                                                                                                 | 4-11       |

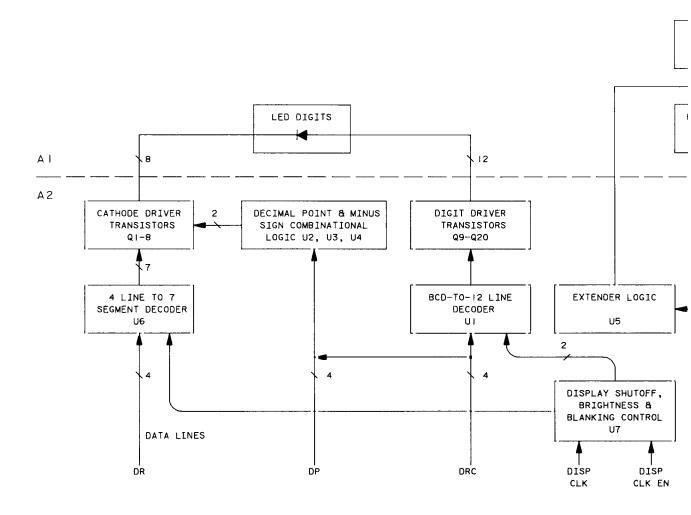

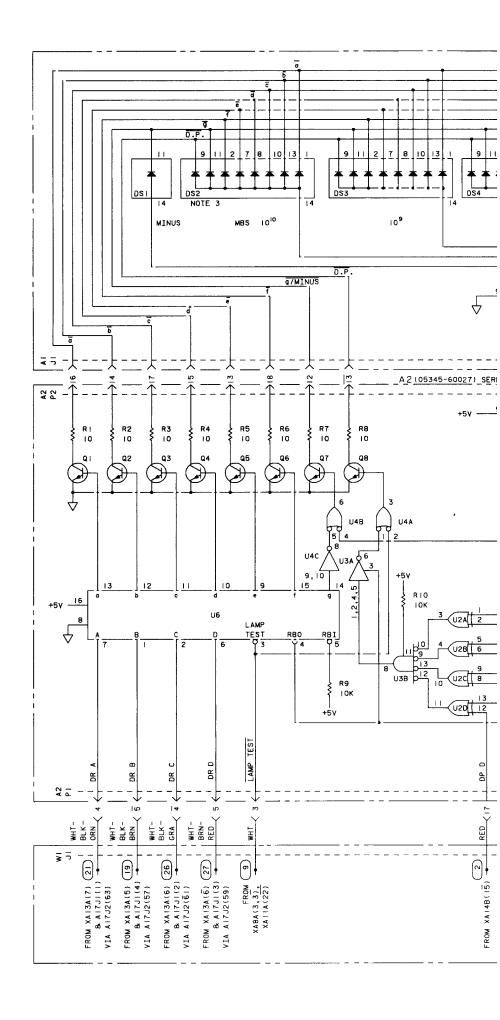

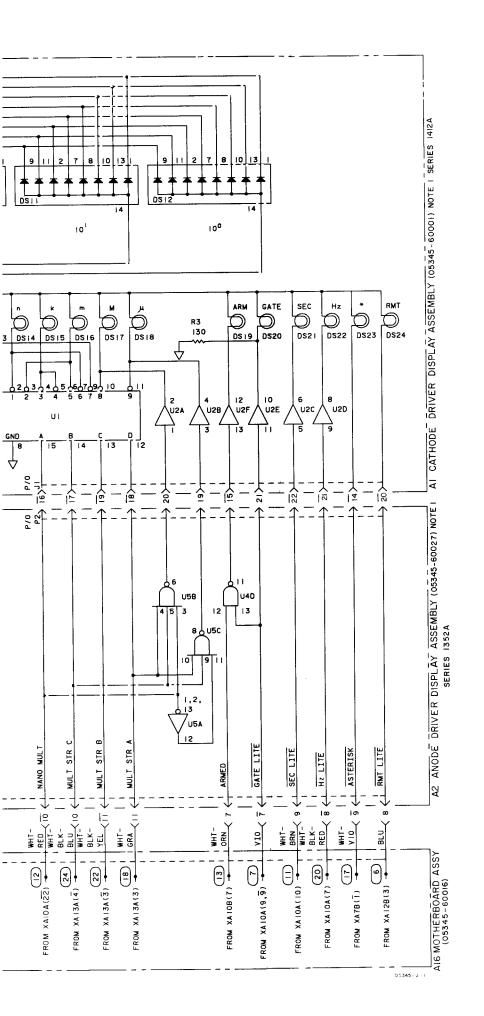

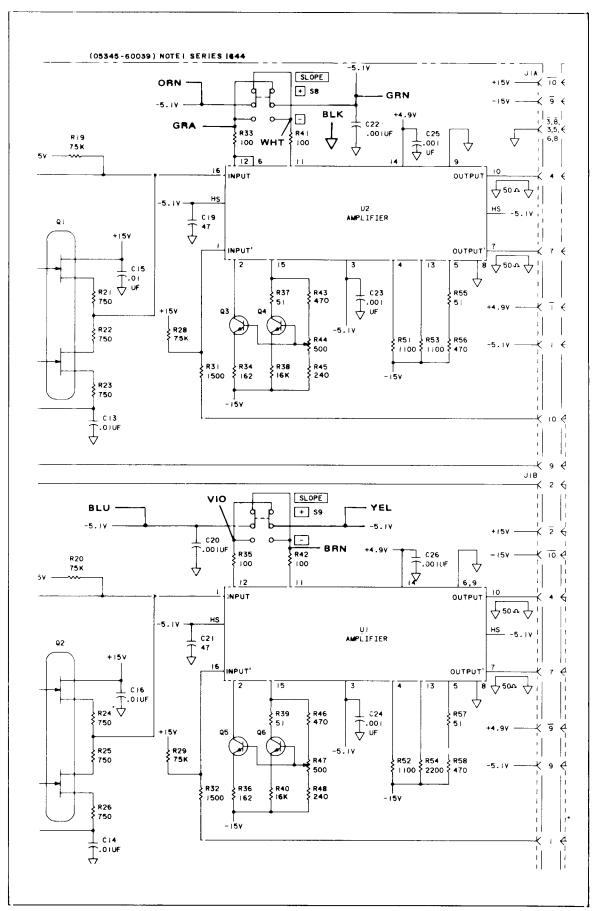

|                    | 4-73.              | A1 and A2 Display Assemblies                                                                                         |            |

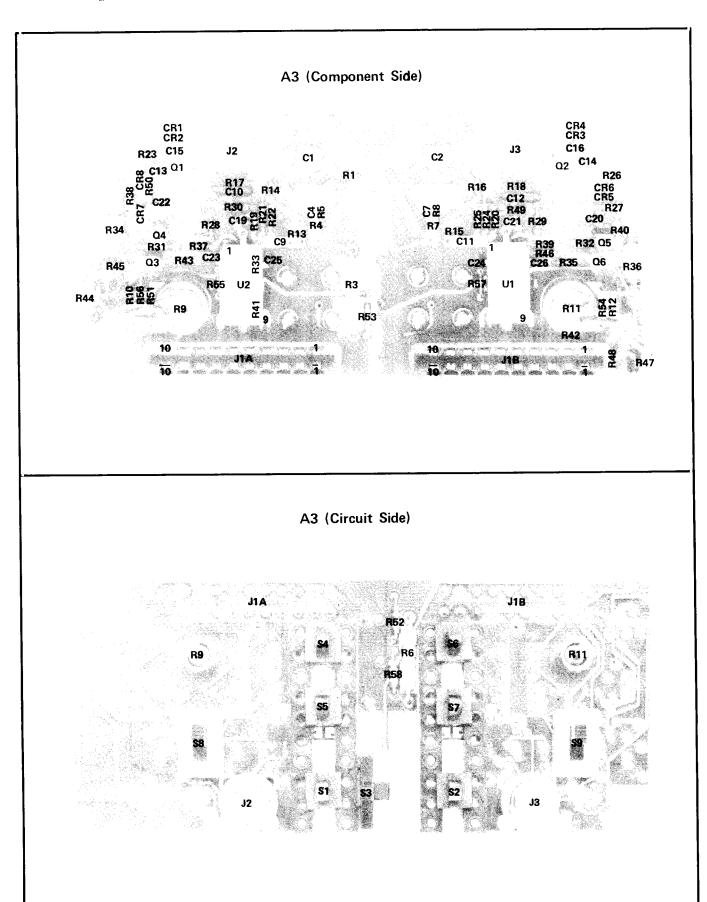

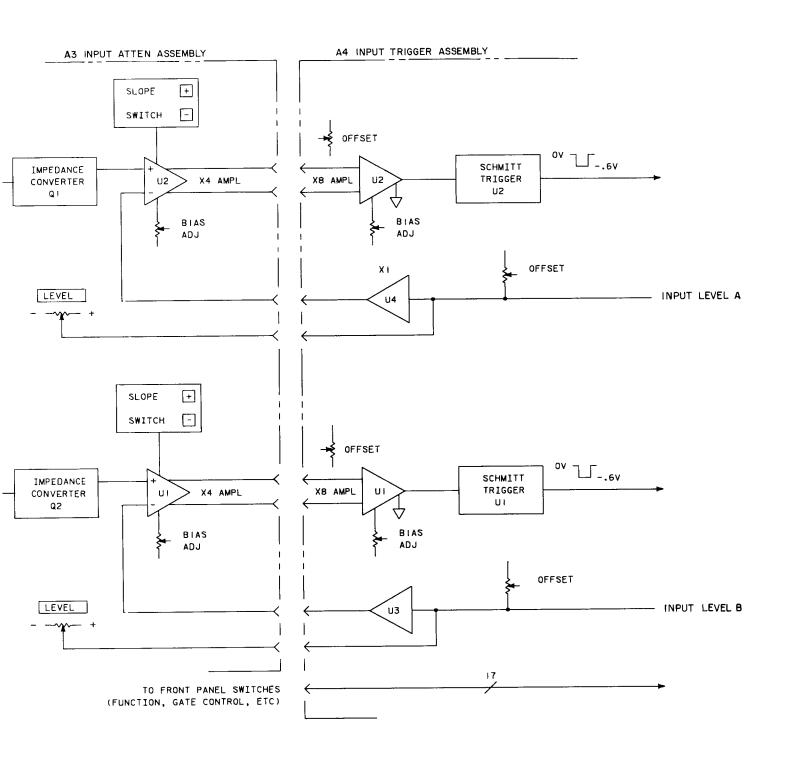

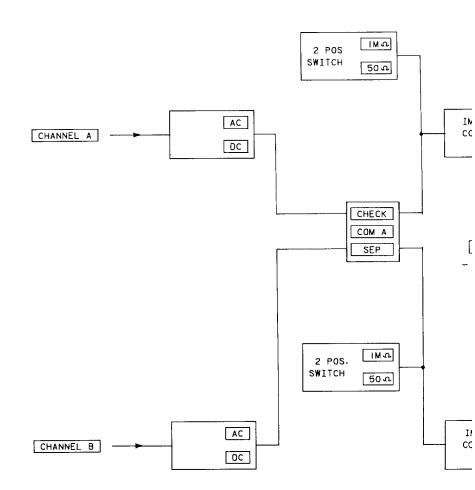

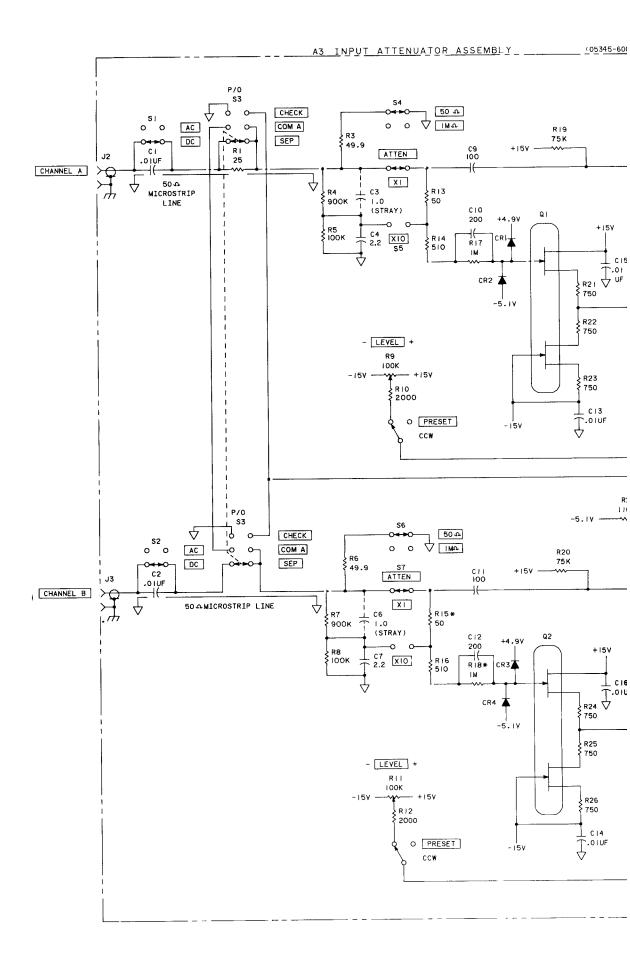

|                    | 4-84.              | A3 Input Attenuator                                                                                                  |            |

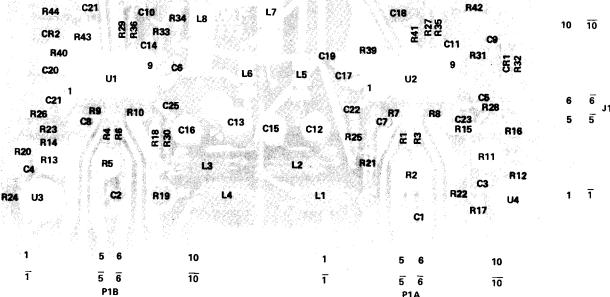

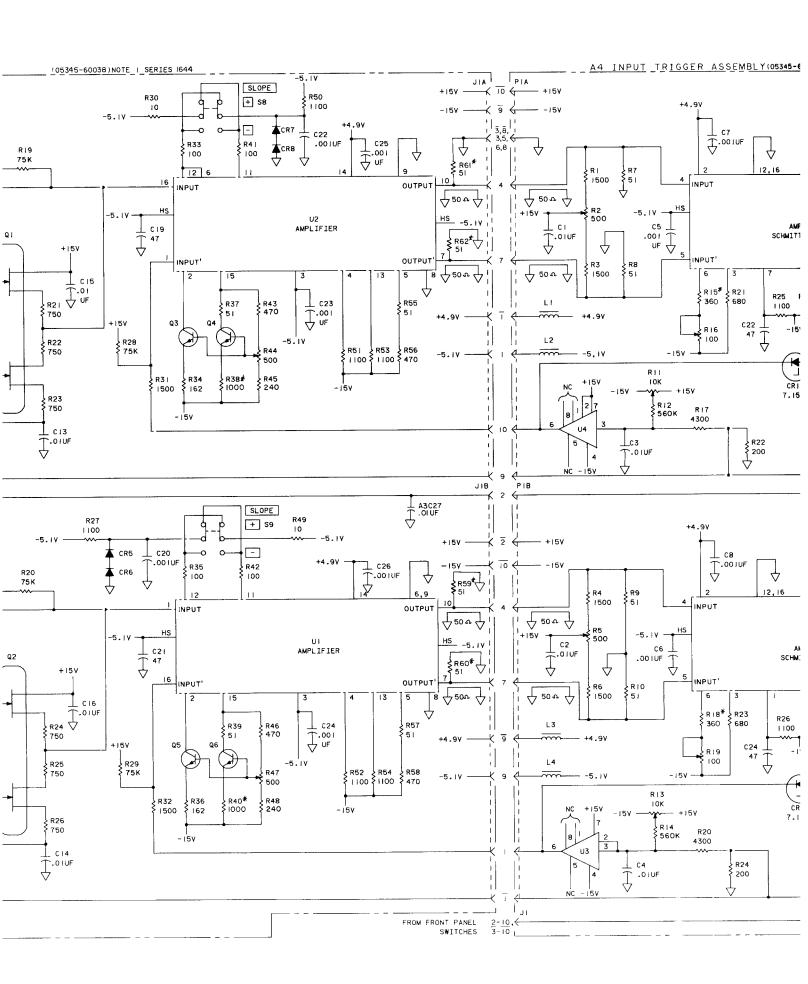

|                    | 4-89.              | A4 Input Trigger                                                                                                     |            |

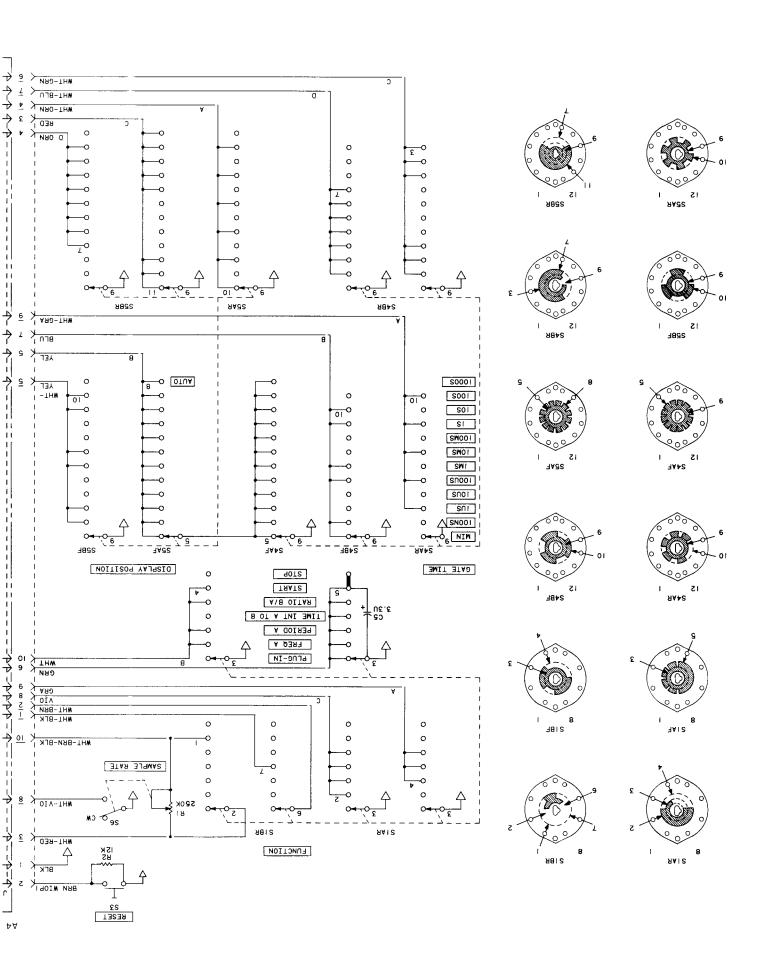

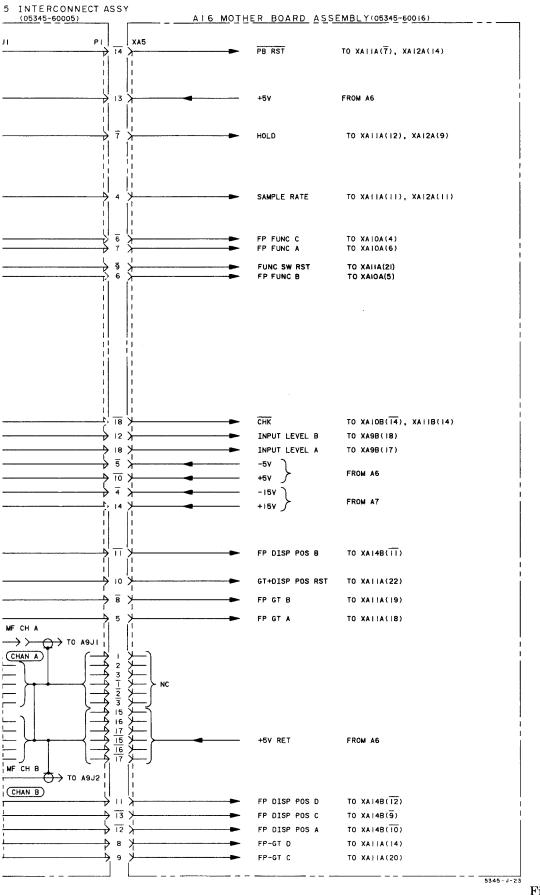

|                    | 4-93.              | A5 Front Panel Interconnect                                                                                          |            |

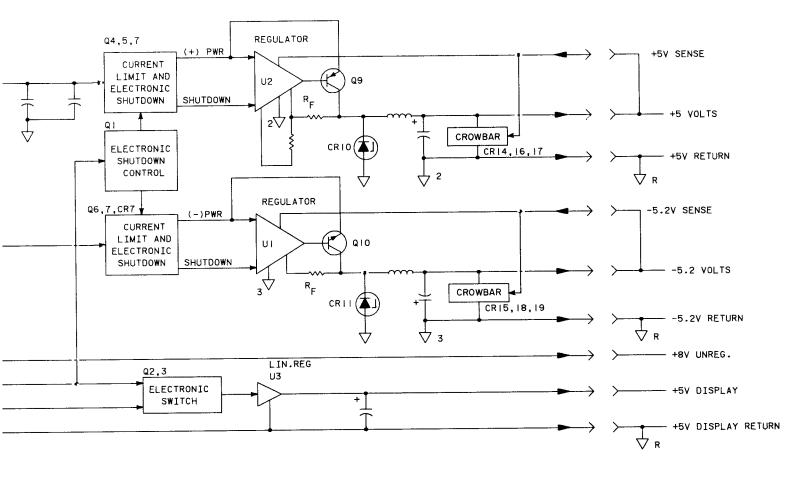

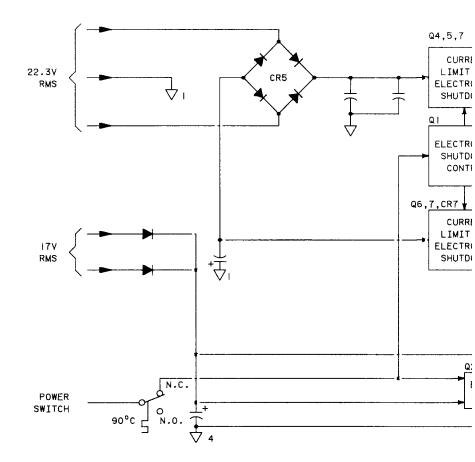

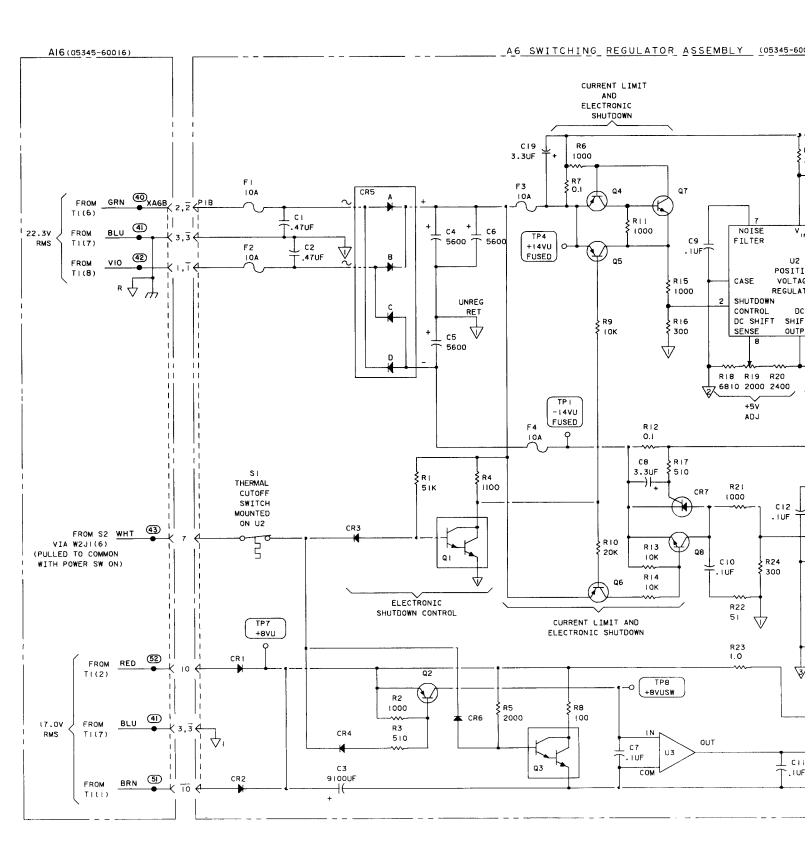

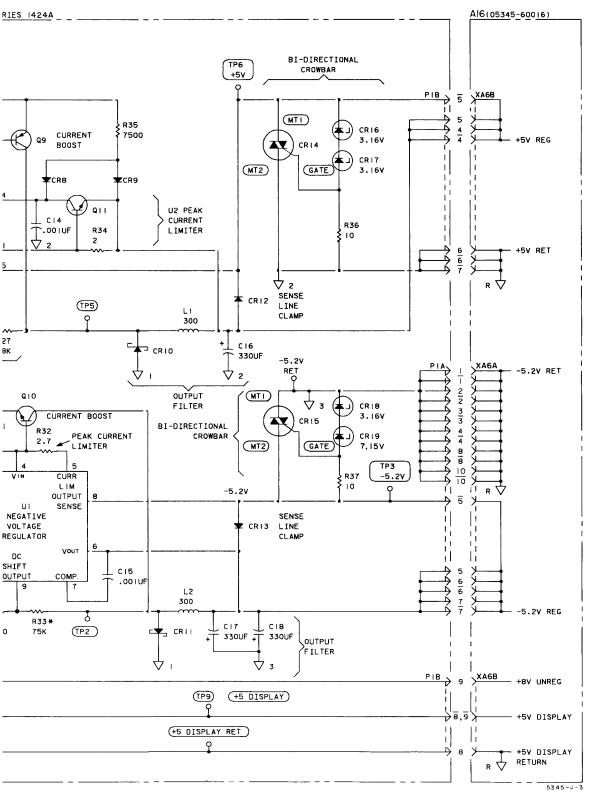

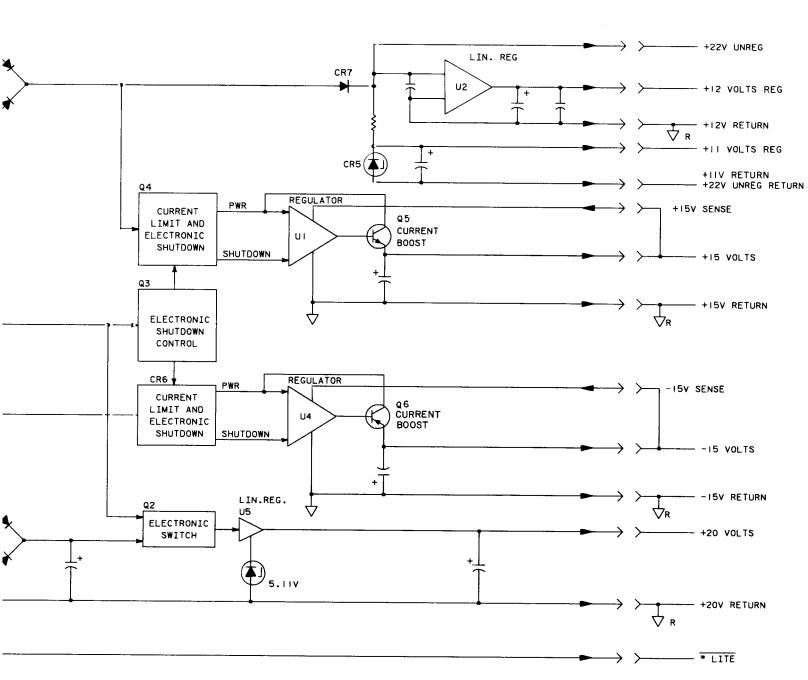

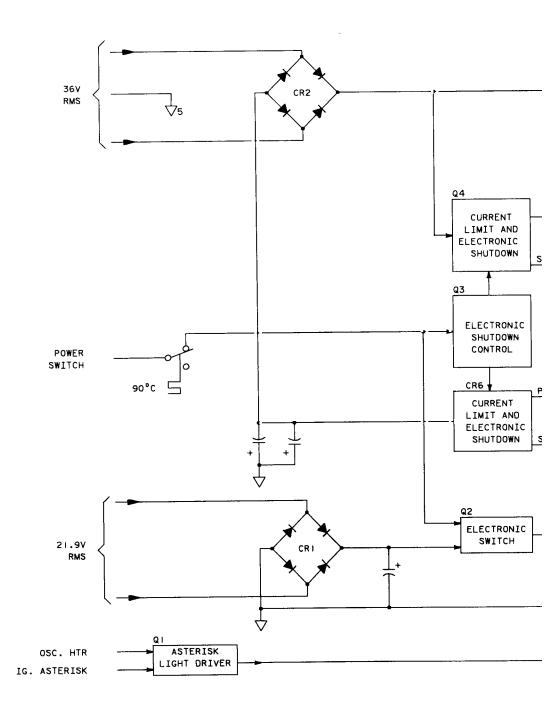

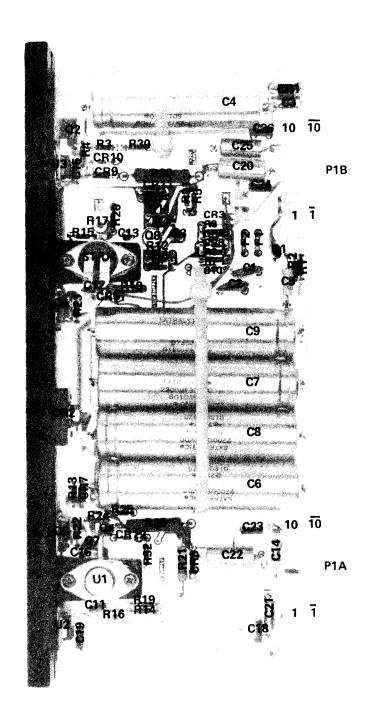

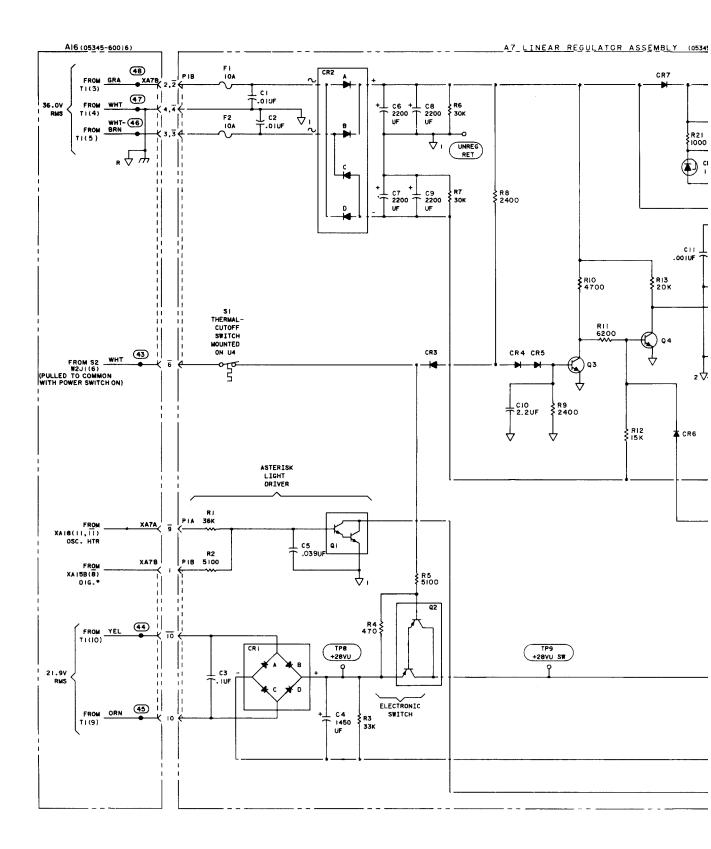

|                    | 4-95.<br>4-105.    | A6 Switching Regulator A7 Linear Regulator                                                                           |            |

|                    | 4-105.<br>4-116.   | 어느 아이들 것 이 생생님, 아이들 때문 프랑이트, 아이들 중요에 대한 사람들이 되었다. 그는 아이들 때문에 가는 사람들이 되었다.                                            | 4-15       |

|                    | 4-132              |                                                                                                                      |            |

|                    | 4-146.             | 있다. 그는 마음을 보고 발생하는 보고 있다면 사람들이 있다면 하다는 사람들이 되었다. 그는 사람들이 그리고 있는 것이 되었다. 그는 사람들이 되었다. 그는 사람들이 되었다. 그는 사람들이 되었다.       |            |

|                    | 4-161.             |                                                                                                                      |            |

|                    | 4-176.             | 그는 그 아니라 하나 보다 나는 사람들이 되는 사람들이 되는 것이 없는 것이다. |            |

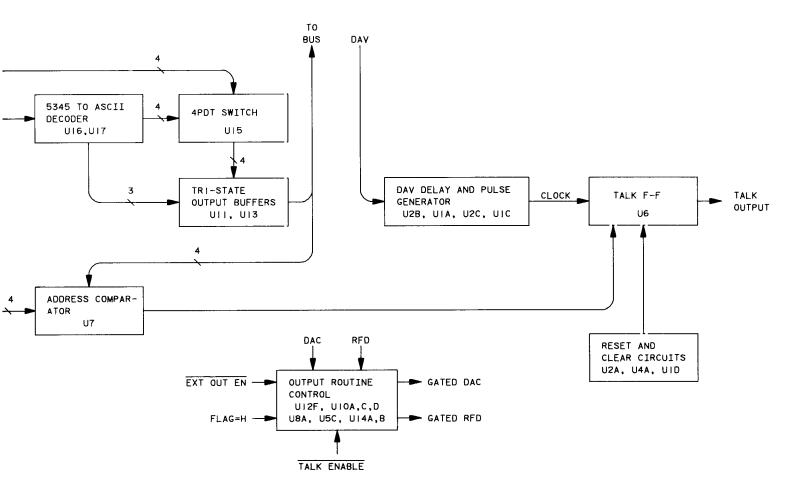

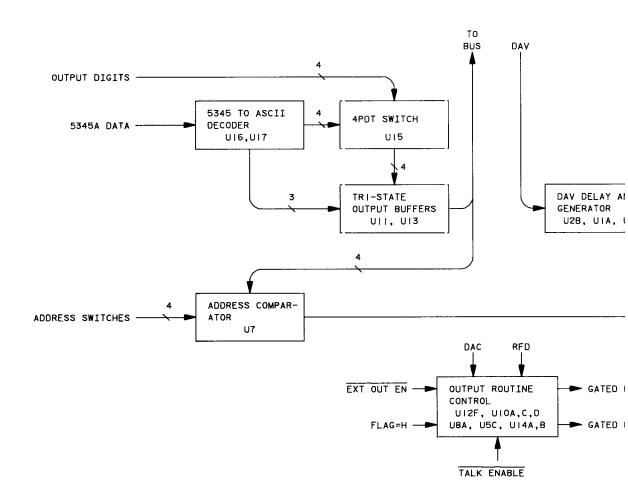

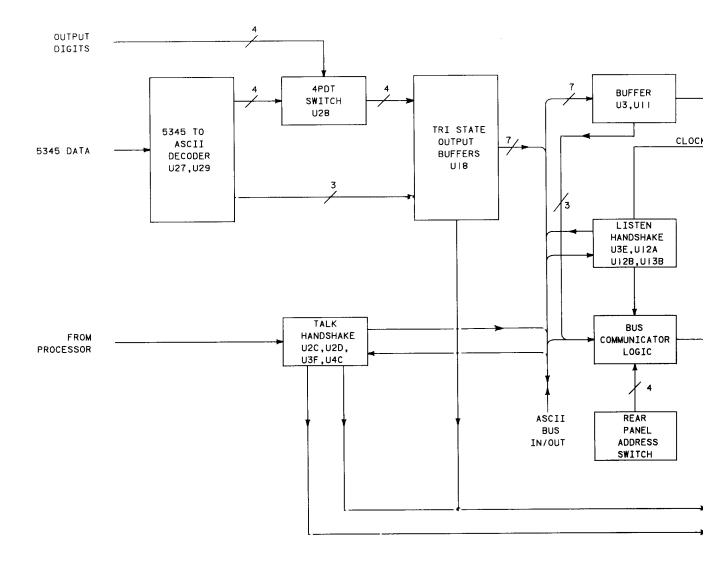

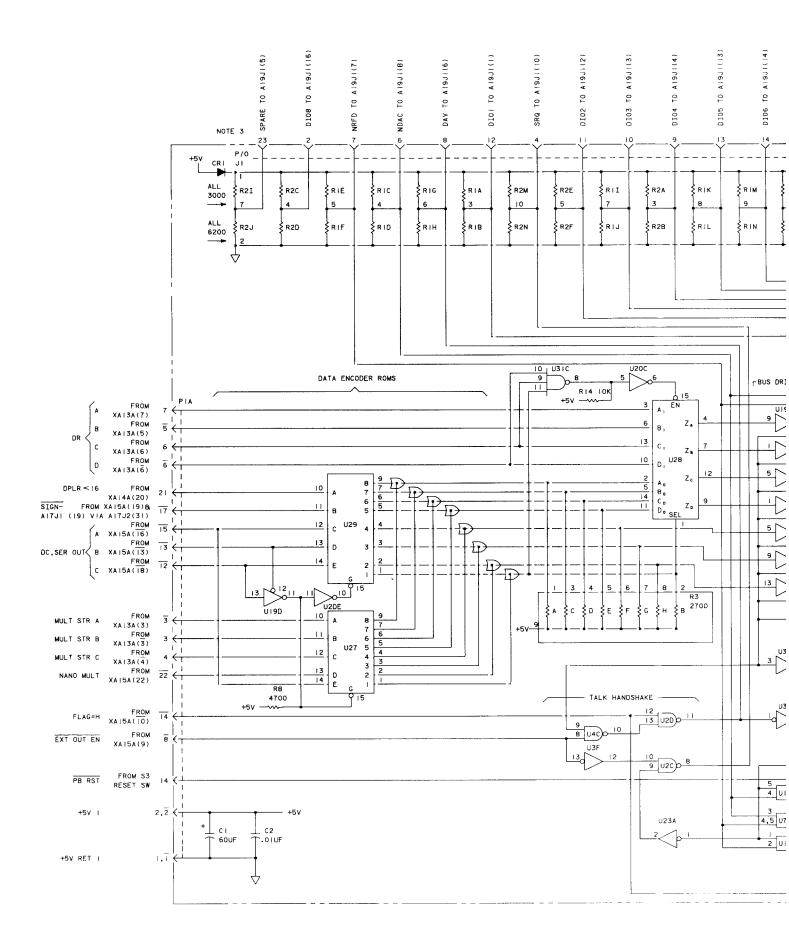

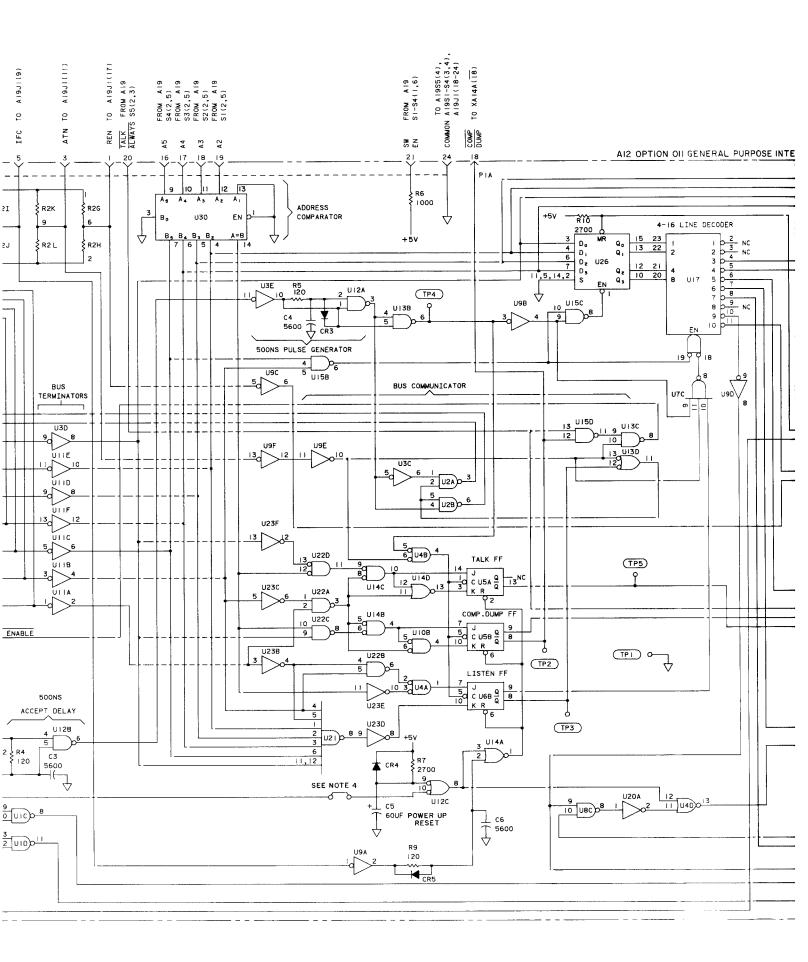

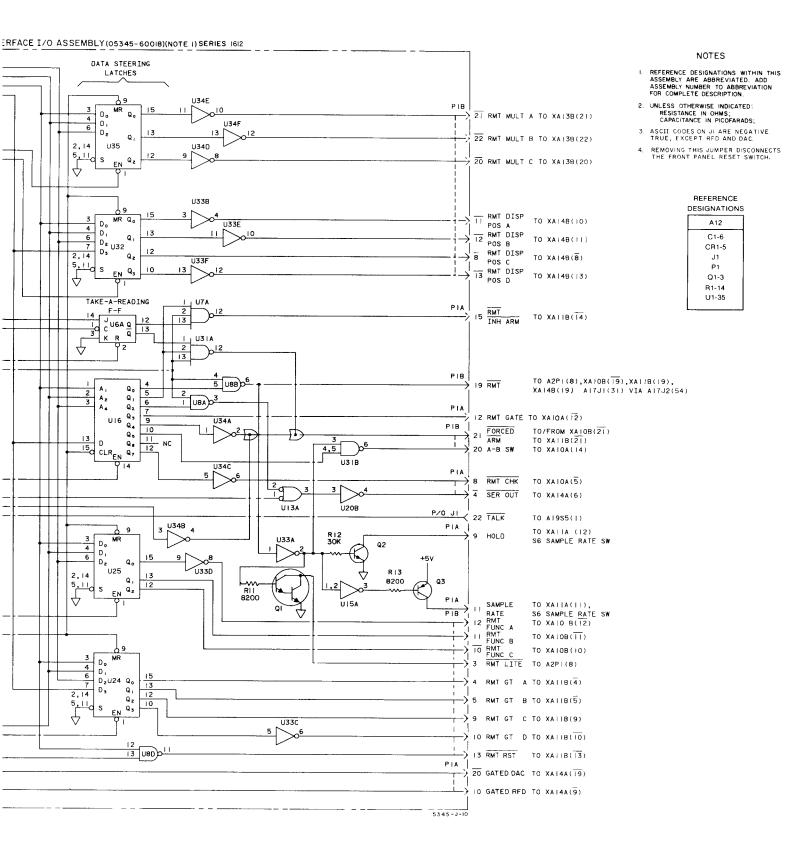

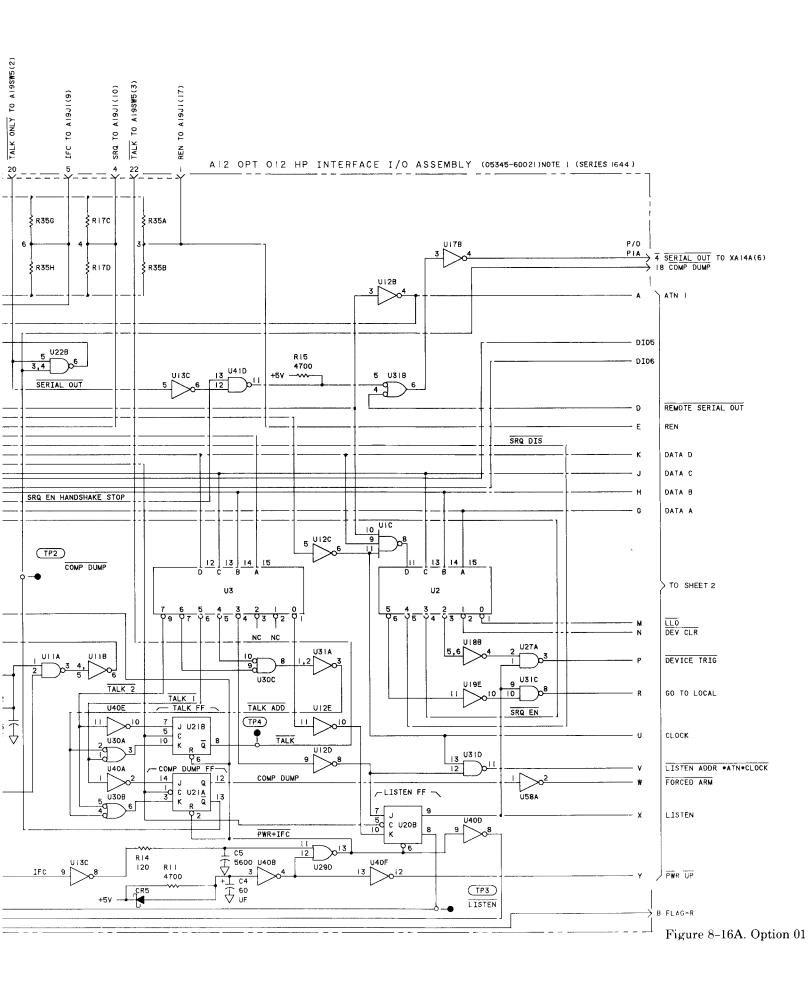

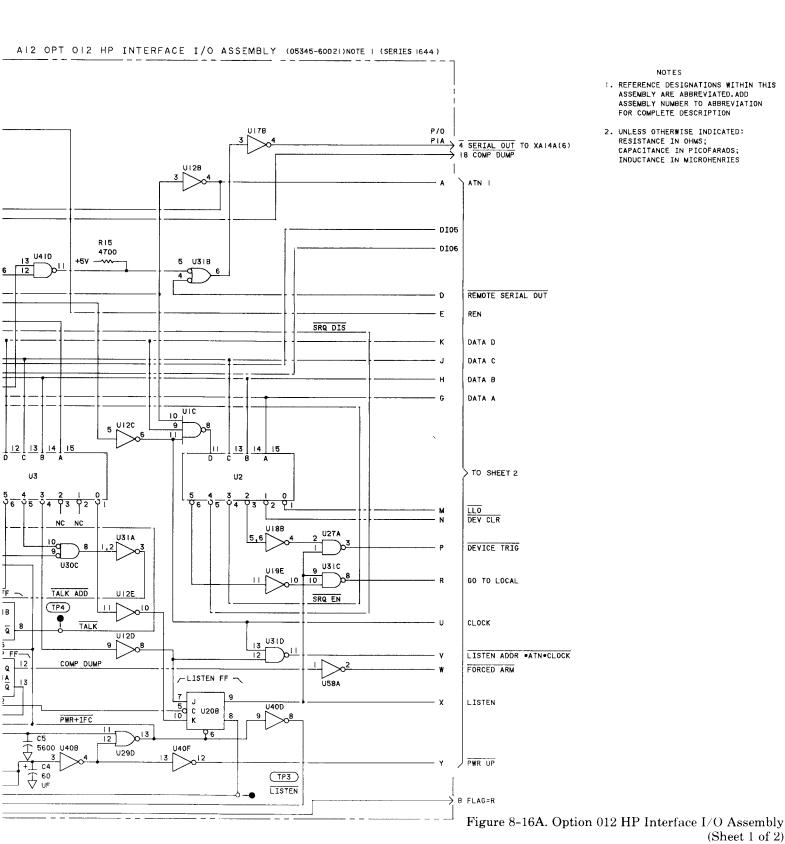

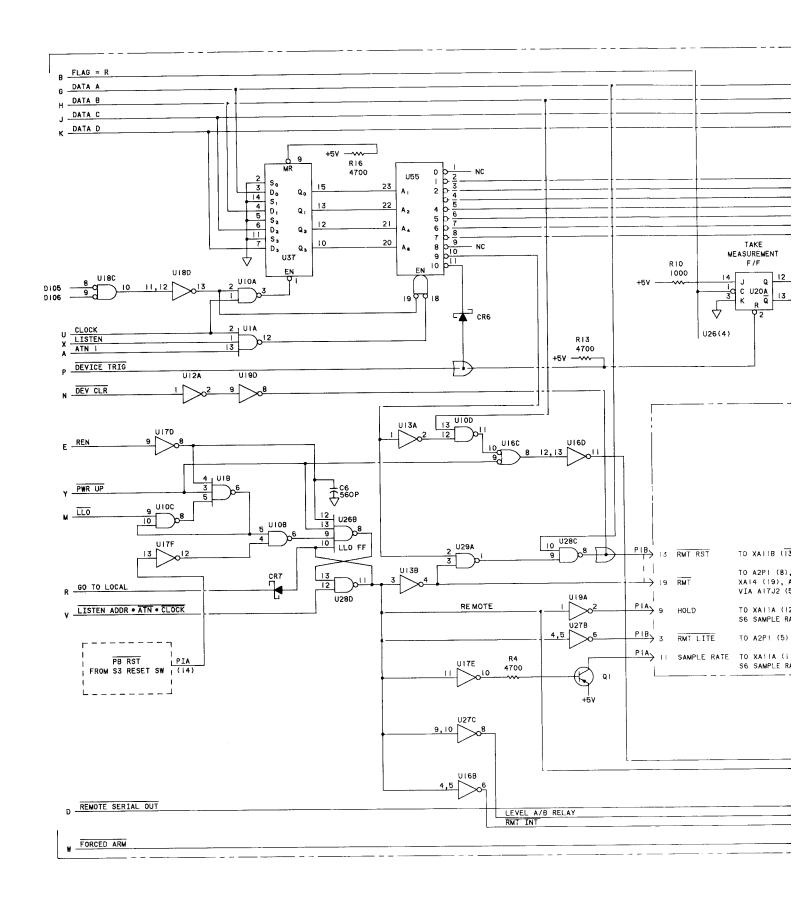

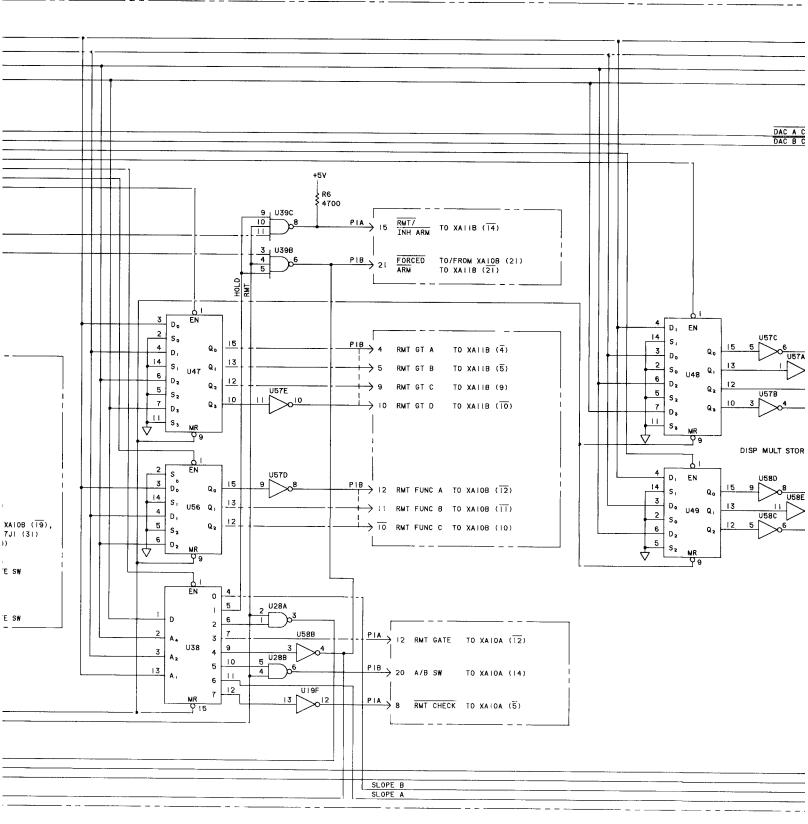

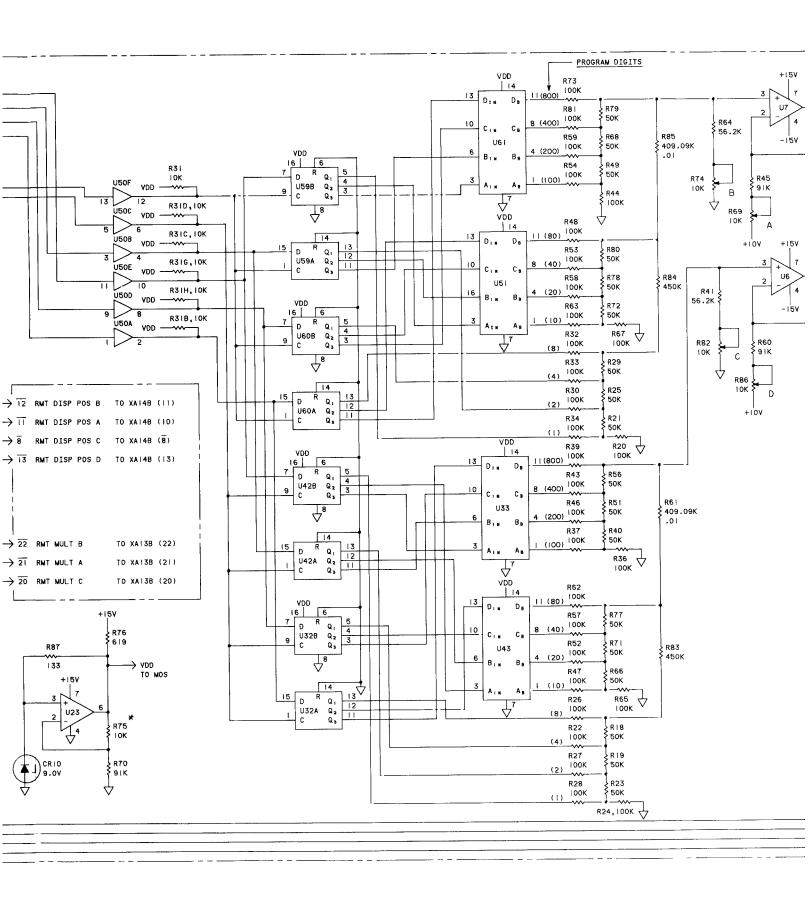

|                    | 4-183.             | A12 Option 011 General Purpose Interface I/O                                                                         | 4-25       |

|                    | 4-196.             |                                                                                                                      |            |

|                    | 4-219.             |                                                                                                                      |            |

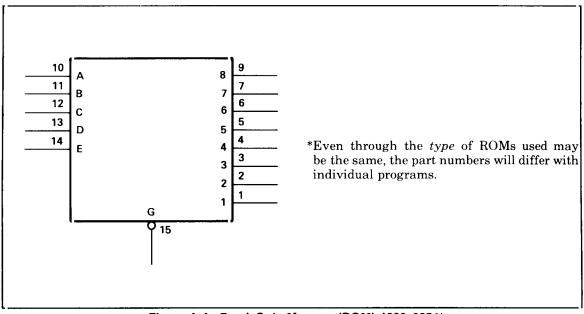

|                    | 4-241.             | A15 ROM,                                                                                                             | 4-40       |

|                    | 4-271              |                                                                                                                      |            |

|                    | 4-278              |                                                                                                                      |            |

|                    | 4-275.             |                                                                                                                      |            |

|                    | 4-277.<br>4-281.   |                                                                                                                      |            |

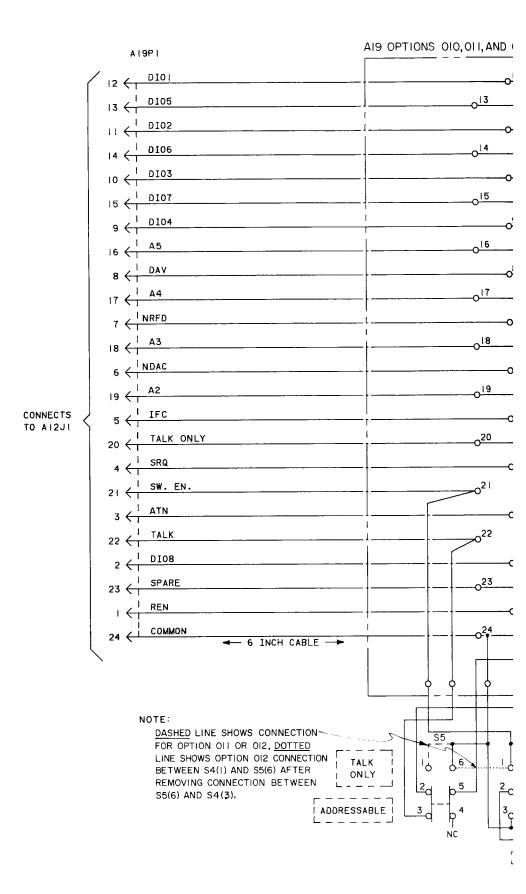

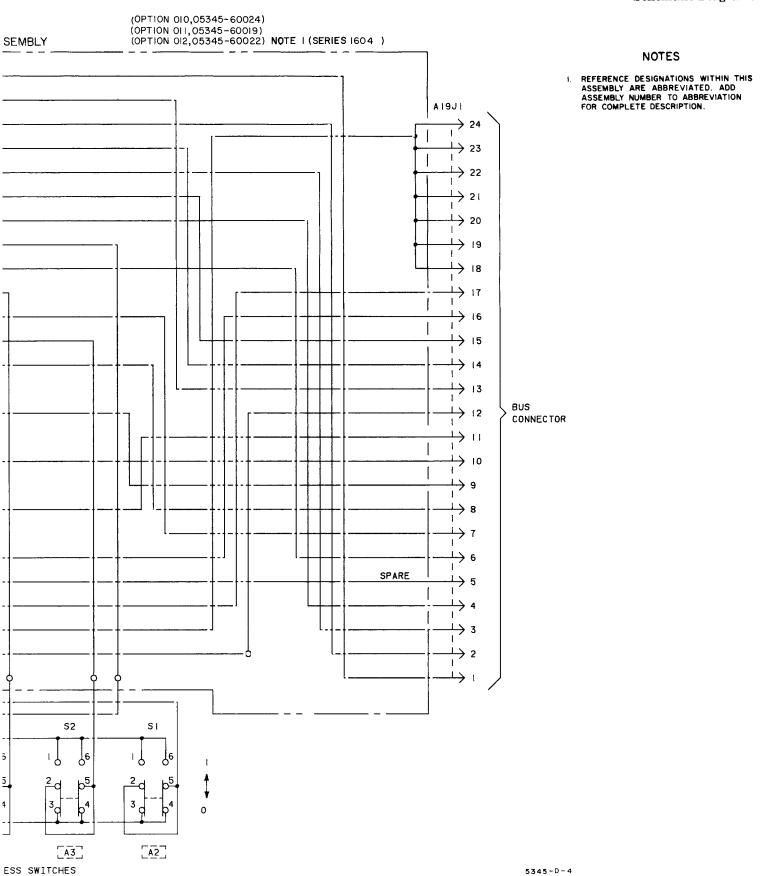

|                    | <del>4-</del> 201. | A19 Oppor 970, 911 Interrace Panel                                                                                   |            |

# **TABLE OF CONTENTS (Continued)**

| Section |              |                                                   | Page         |

|---------|--------------|---------------------------------------------------|--------------|

| V       | MAIN         | VTENANCE AND SERVICE                              | 5-1          |

|         | 5-1.         | Introduction                                      | 5-1          |

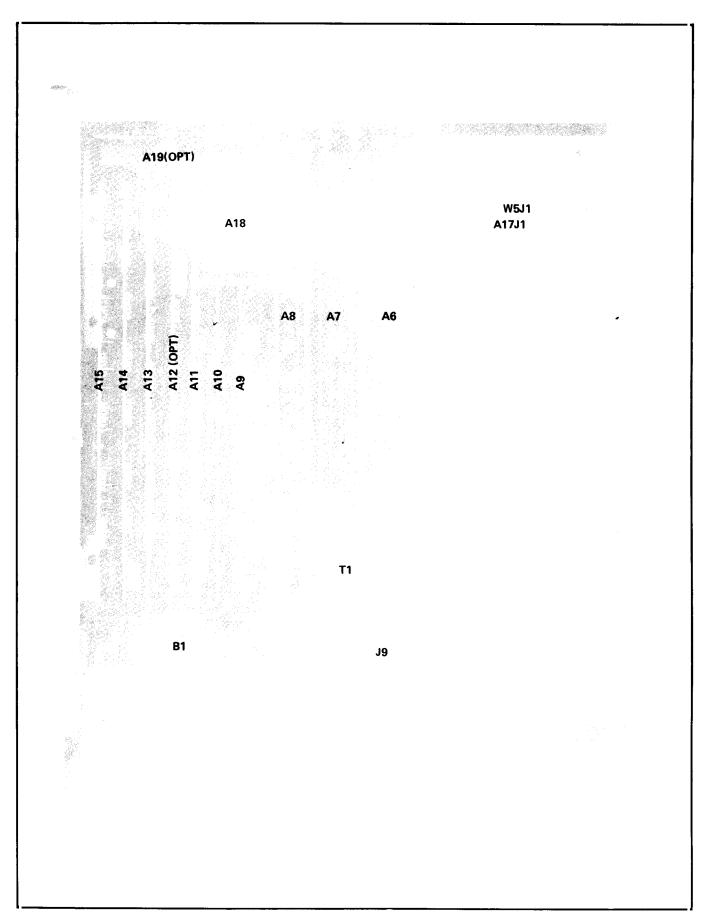

|         | 5-3.         | Assembly Designations                             |              |

|         | 5-5.         | Test Equipment                                    | 5–1          |

|         | 5-7.         | Adjustments and In-Cabinet Performance Check      | 5-1          |

|         | <b>5-9</b> . | Periodic Maintenance                              | 5-1          |

|         | 5-11.        | Overall Troubleshooting                           | 5–2          |

|         | 5-13.        | Board Replacement Method (Kit No. 10597A)         | 5–2          |

|         | 5-16.        | Trouble Isolation Method                          | 5-2          |

|         | 5-20.        | Troubleshooting Aids                              | 5 <b>-</b> 3 |

|         | 5-22.        | 5345A ASM Tester (K13-59992A)                     | 5–3          |

|         | 5-24.        | Extender Board Kit (10595A)                       |              |

|         | 5-26.        | Special Test Board (05345-60200)                  | 5-4          |

| VI      | REPI         | ACEABLE PARTS                                     | 6-1          |

| **      | 6-1.         | Introduction                                      | 6-1          |

|         | 6-4.         | Ordering Information                              |              |

|         | 6-7.         | HP Part Number Organization                       |              |

|         | 6-9          | Component Parts and Materials                     |              |

|         | 6-12.        | General Usage Parts                               | 6–4          |

|         | 6-14.        | Specific Instrument Parts                         |              |

|         |              |                                                   |              |

| VII     |              | ONS AND MANUAL CHANGES                            |              |

|         | 7-1.         | Introduction                                      | 7-1          |

|         | 7-3.         | Options                                           | 7-1          |

|         | 7-5.         | Field Installation of Options                     |              |

|         | 7-8.         | Manual Changes                                    |              |

|         | 7-10.        | Newer Instruments                                 |              |

|         | 7-12.        | Older Instruments                                 | 7-1          |

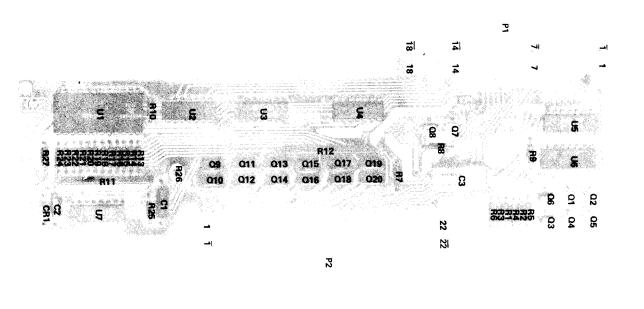

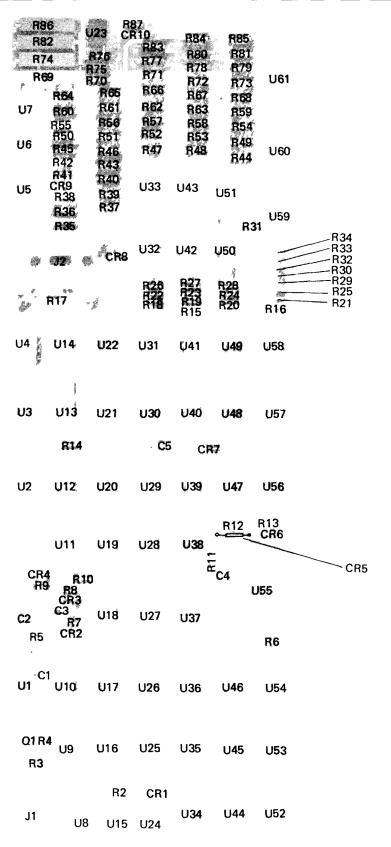

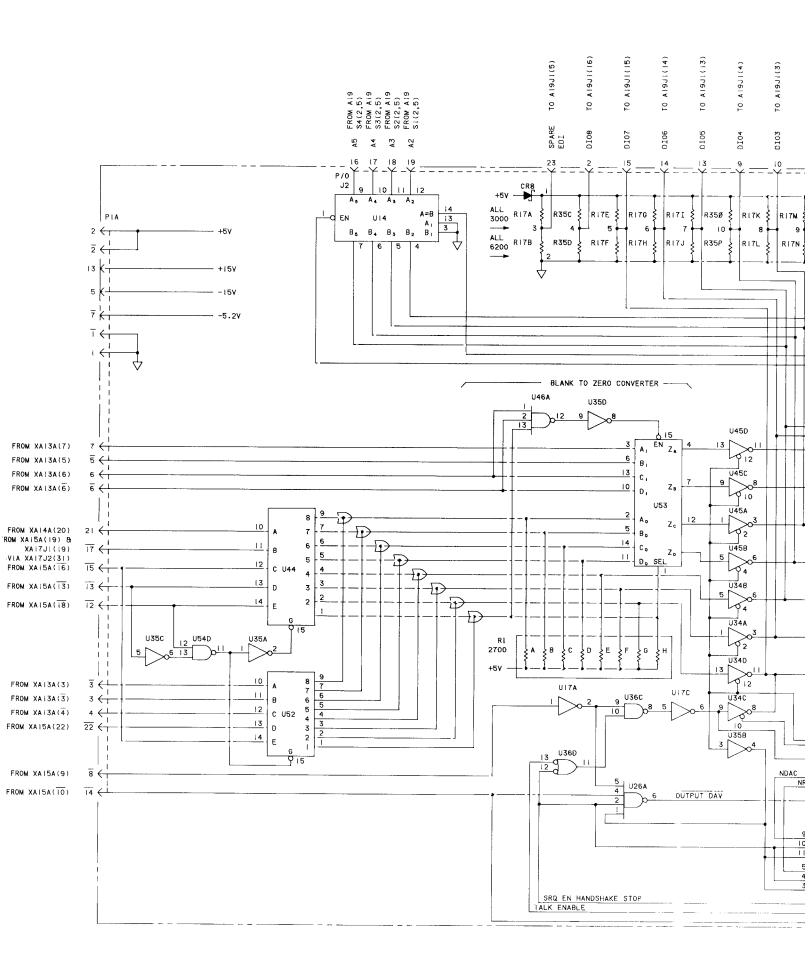

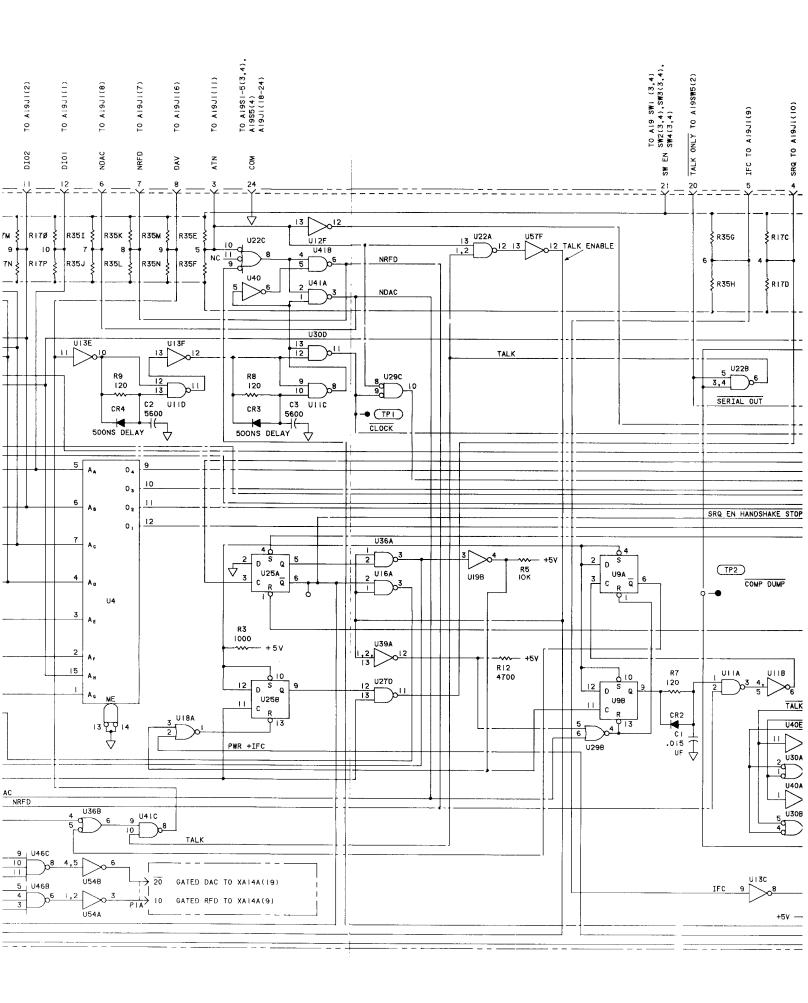

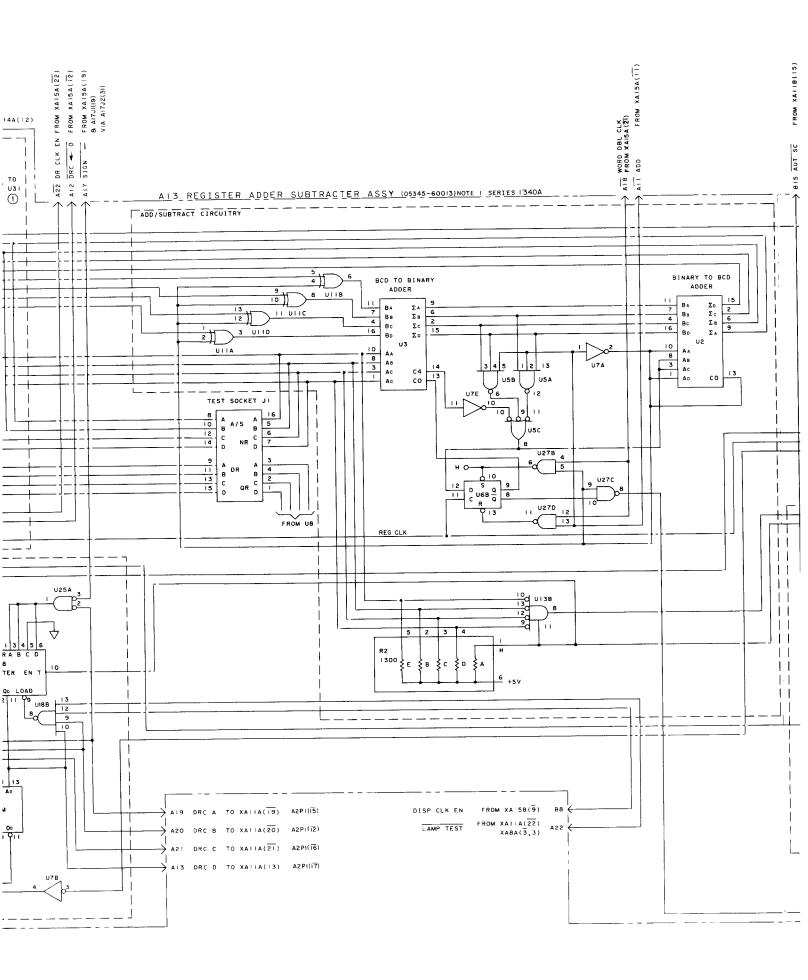

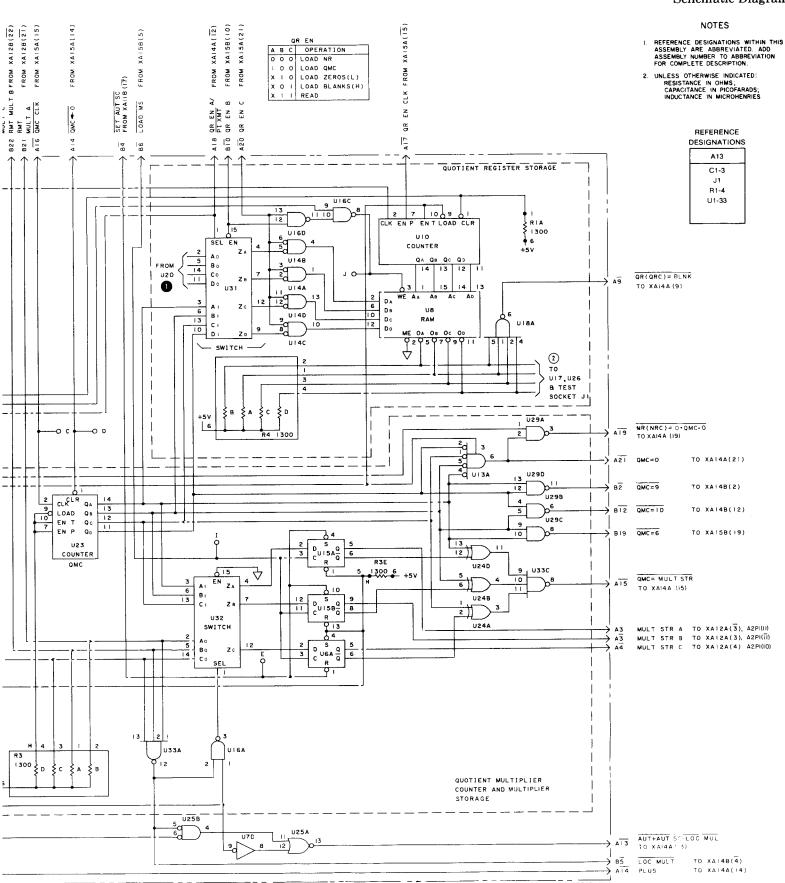

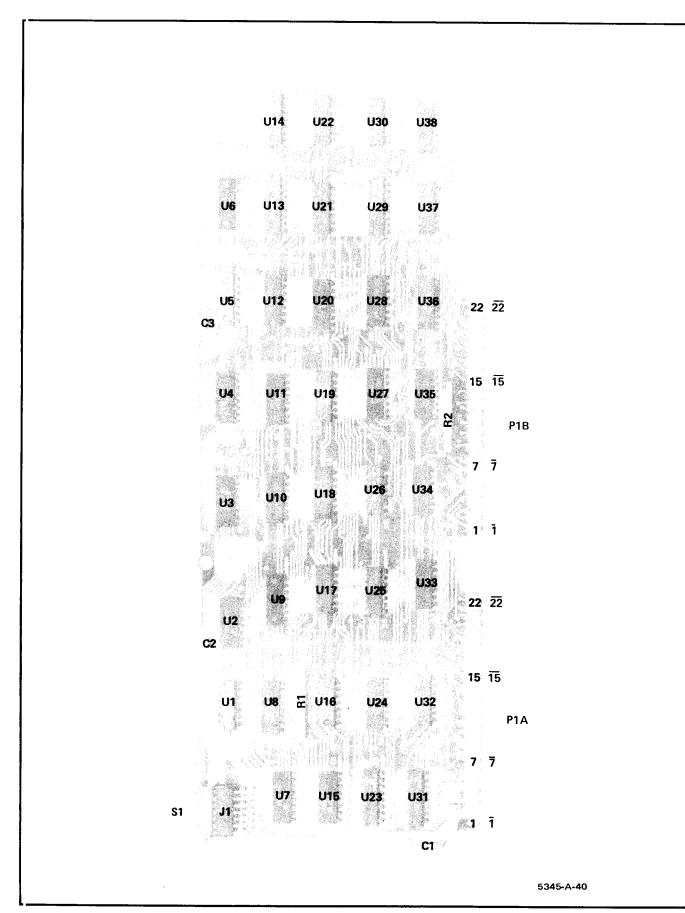

| VIII    | SCHI         | EMATIC DIAGRAMS                                   | 8-1          |

|         | 8-1.         | Schematic Diagrams                                |              |

|         | 8-3.         |                                                   |              |

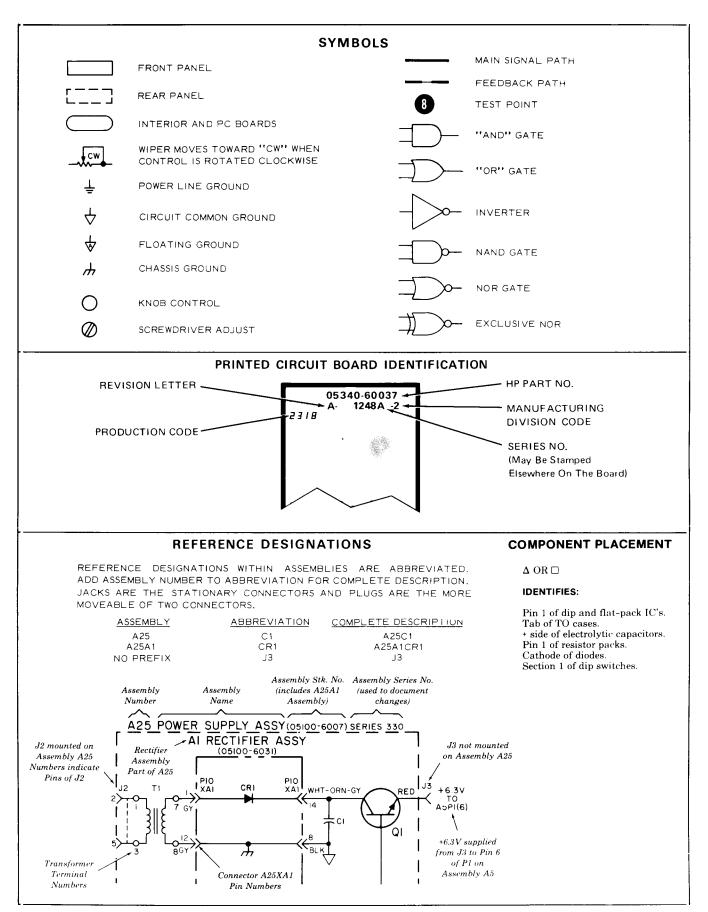

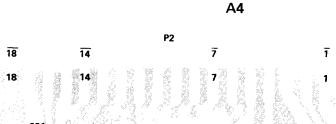

|         |              | Reference Designators                             | 8-1          |

|         | 8-5.         | Reference Designations                            | 8–1          |

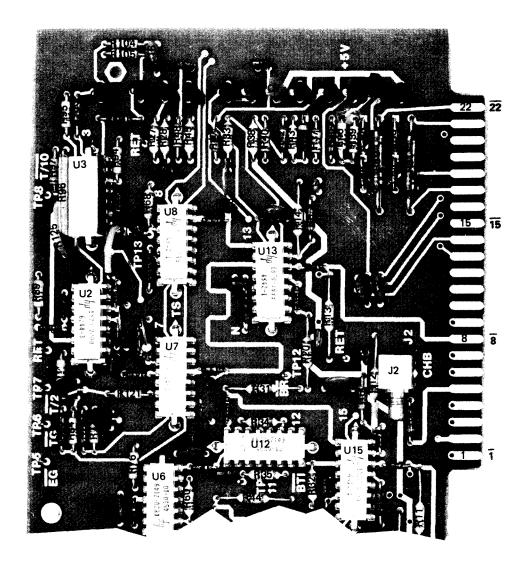

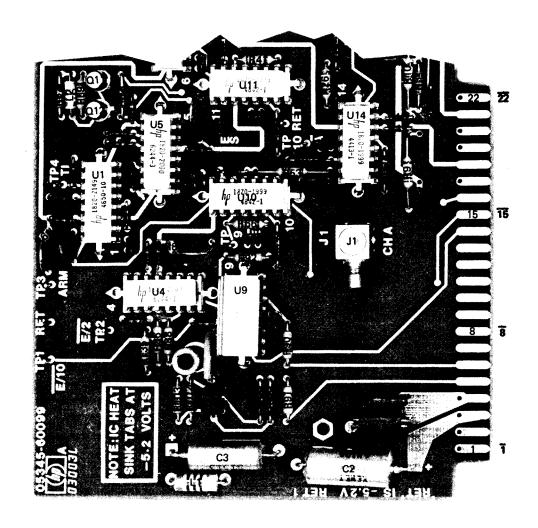

|         | 8-7.         | Identification Markings on Printed-Circuit Boards | 8-1          |

# LIST OF TABLES

| Table        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Page |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1-1.         | Equipment Supplied                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1-1  |

| 1-2.         | Accessories Available                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1-2  |

| 1-3.         | Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1-3  |

| 2-1.         | Relation of ATN and the Transfer Lines (NRFD, NDAC, DAV)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-5  |

| 2-2.         | Talk and Listen Addresses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-9  |

| 2-3.         | Program Code Set, Option 011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-13 |

| 2-4.         | 5345A Program Code Set for 5345A Option 012                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-16 |

| 2-5.         | Universal Commands for Model 5345A Option 012                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-17 |

| 2-6.         | 5345A Output Code Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

| 2-7.         | Program Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 2-8.         | Address Switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| 3-1.         | Scaler Output for Channel A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-4  |

| 3-2.         | Self-Check                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

| 4-1.         | A9 Control Lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| <b>4-2</b> . | ROM Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-29 |

| 4-3.         | ROM Outputs (1816–0254) U29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| 4-4.         | ROM Outputs (1816-0255) U27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-31 |

| 4-5.         | Commands for Processor Timing Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-42 |

| 5-1.         | Assembly Designations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-1  |

| 5-2.         | Recommended Test Equipment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5-2  |

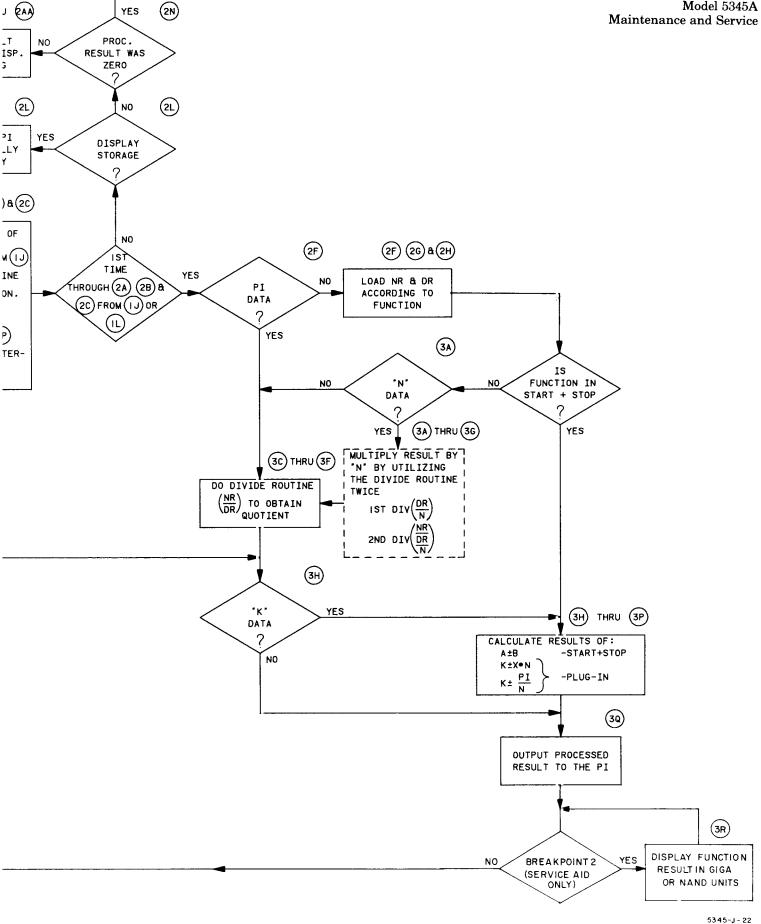

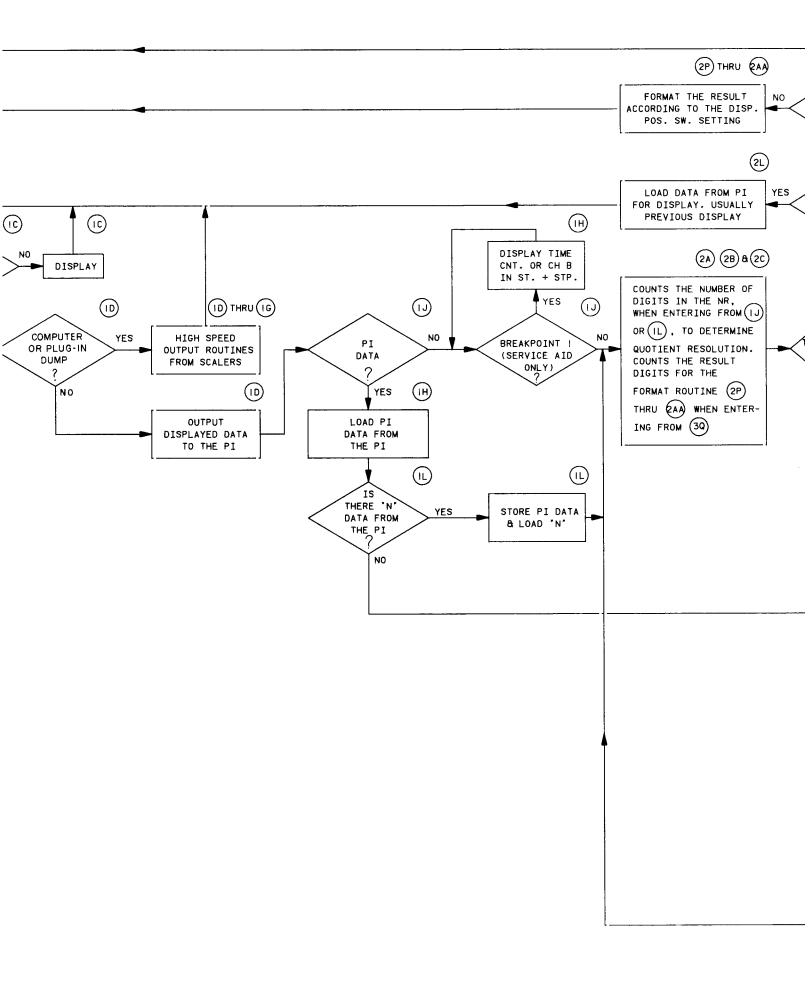

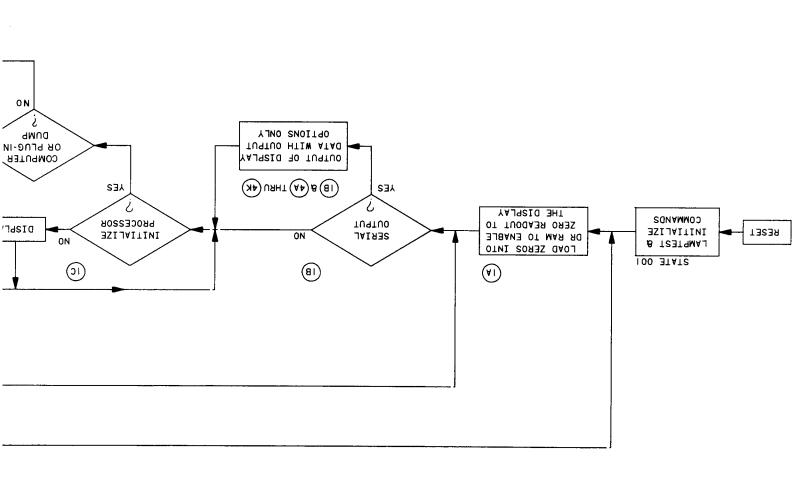

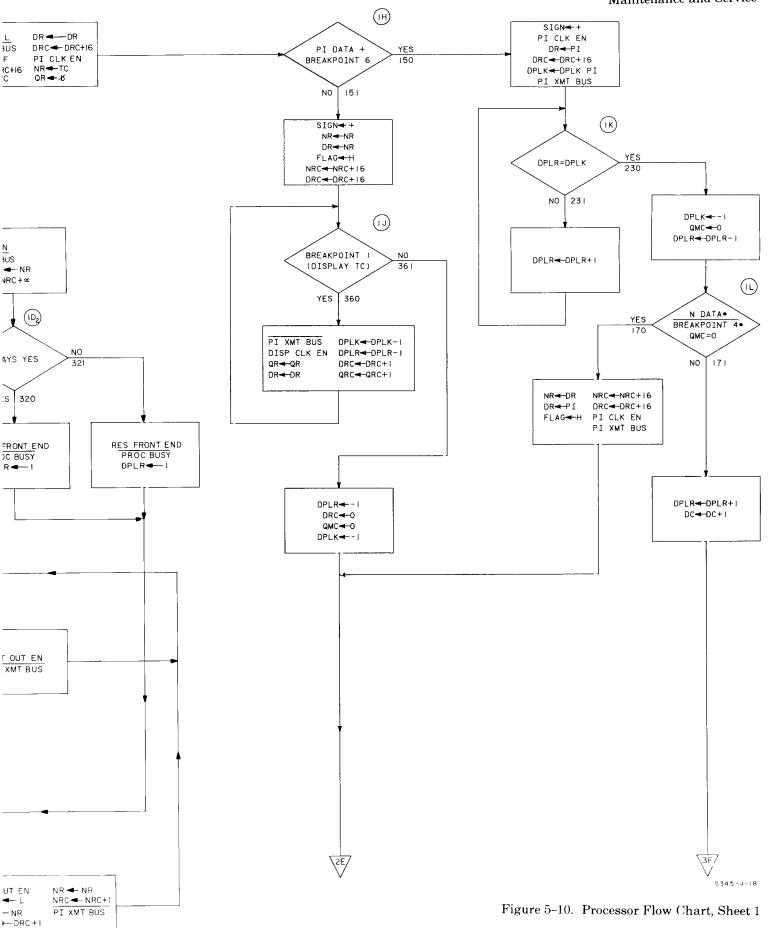

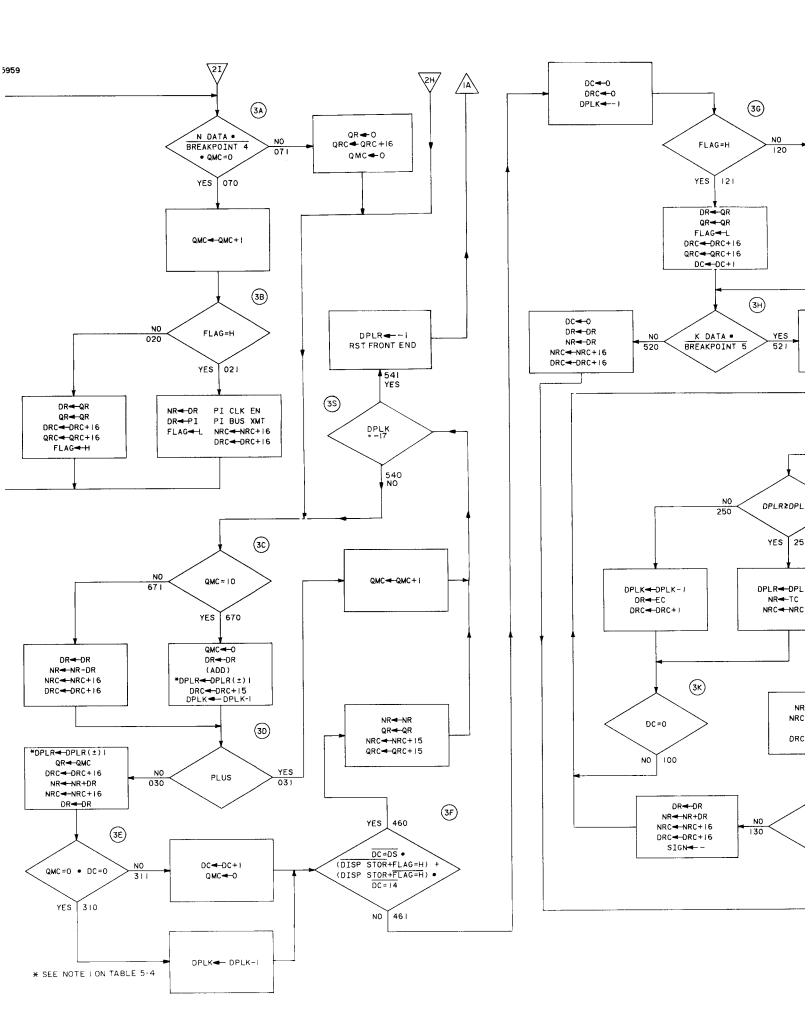

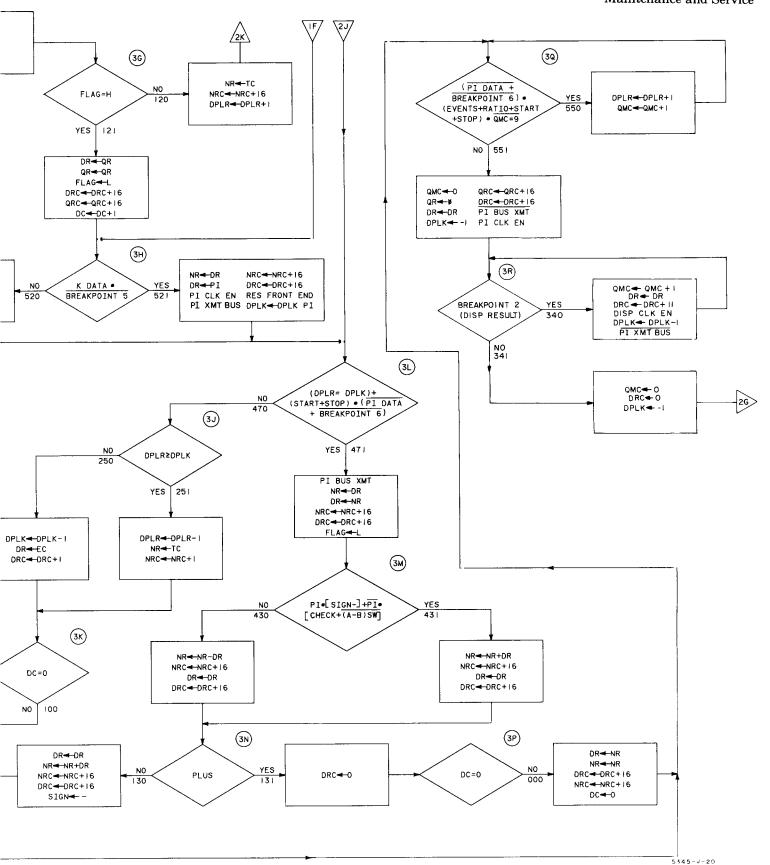

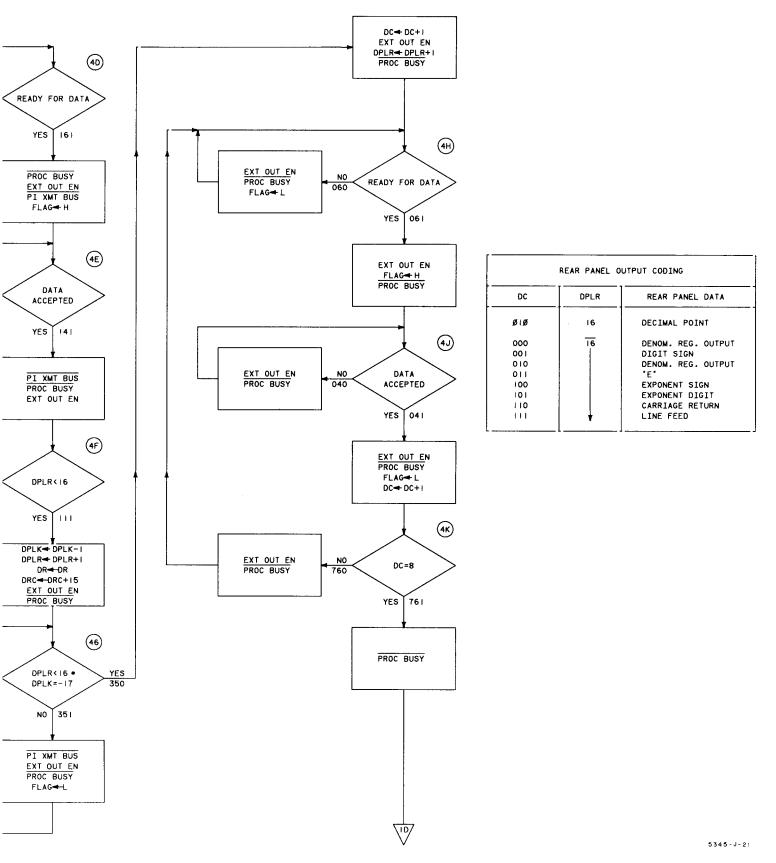

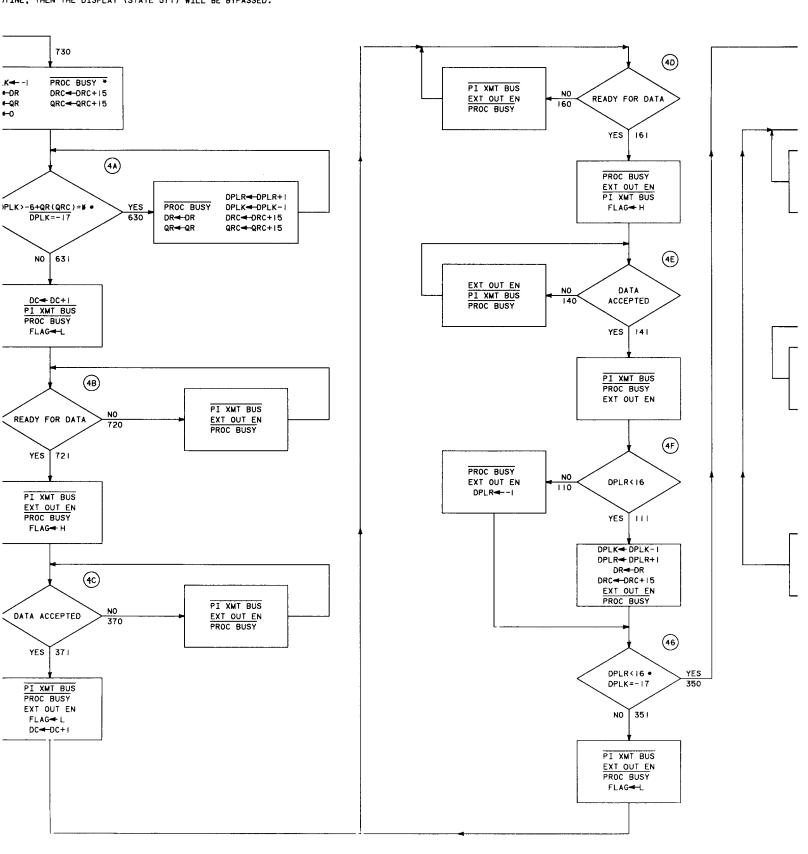

| 5-3.         | Processor Flow Test Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5-18 |

| 5-4.         | Command Source Listing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

| 5-5.         | In-Cabinet Performance Check                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-42 |

| 5-6.         | Adjustment Procedures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-50 |

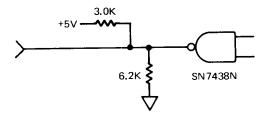

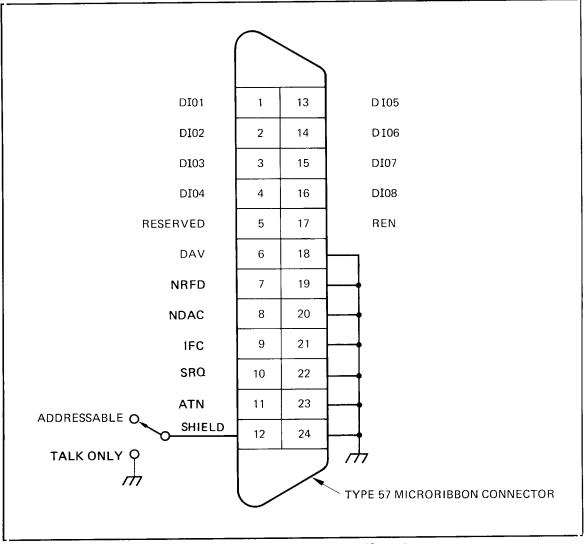

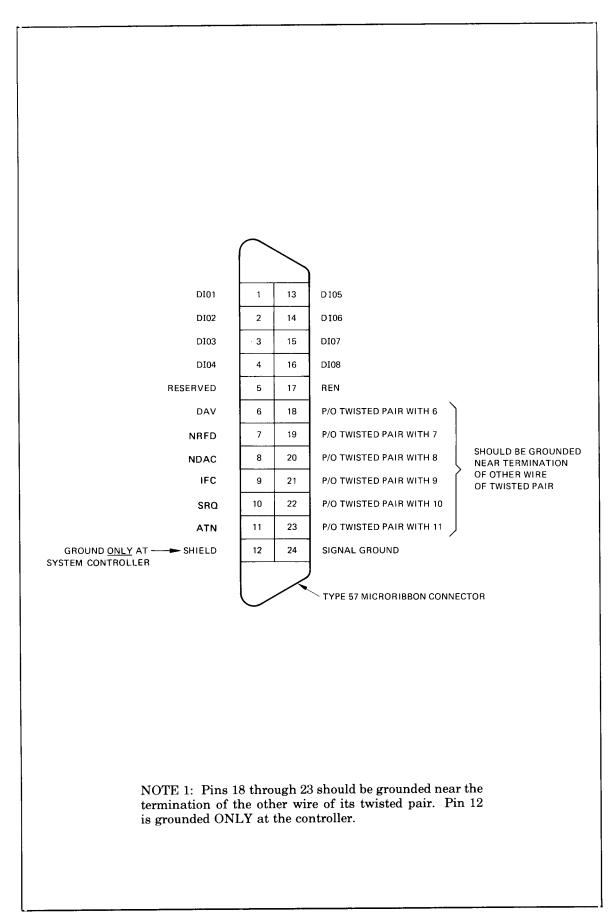

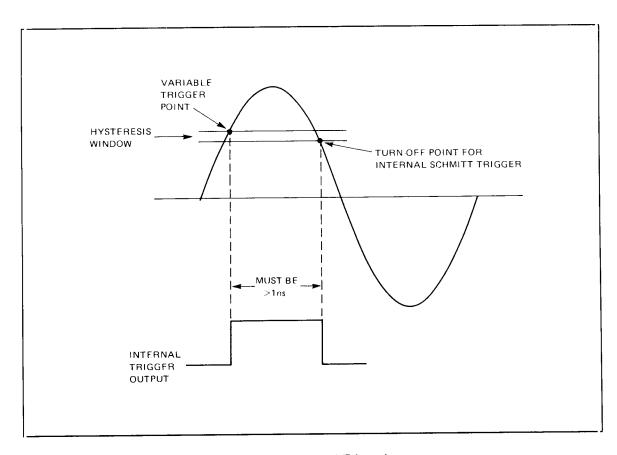

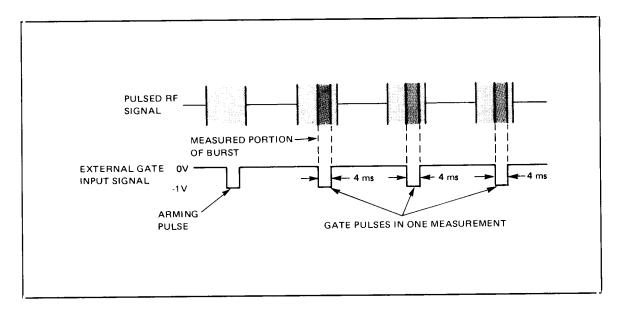

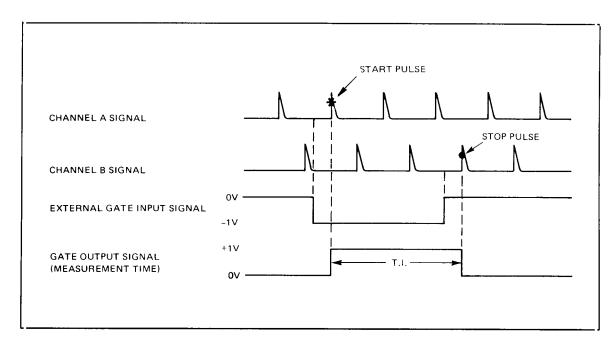

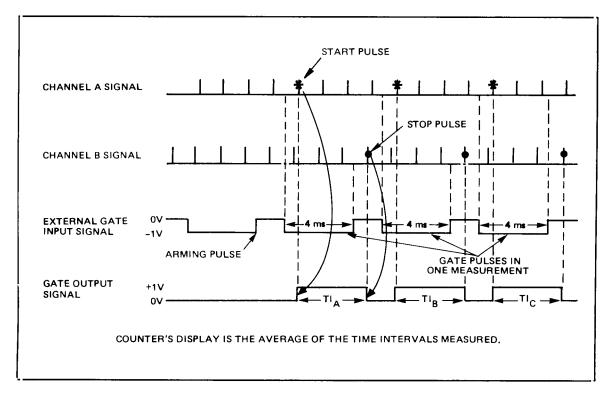

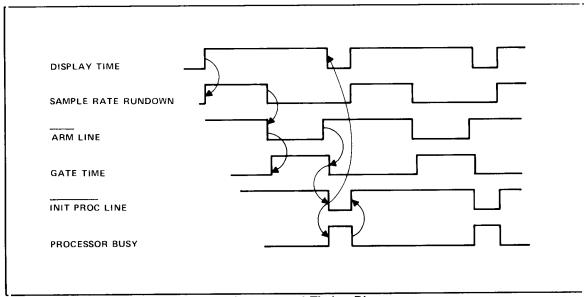

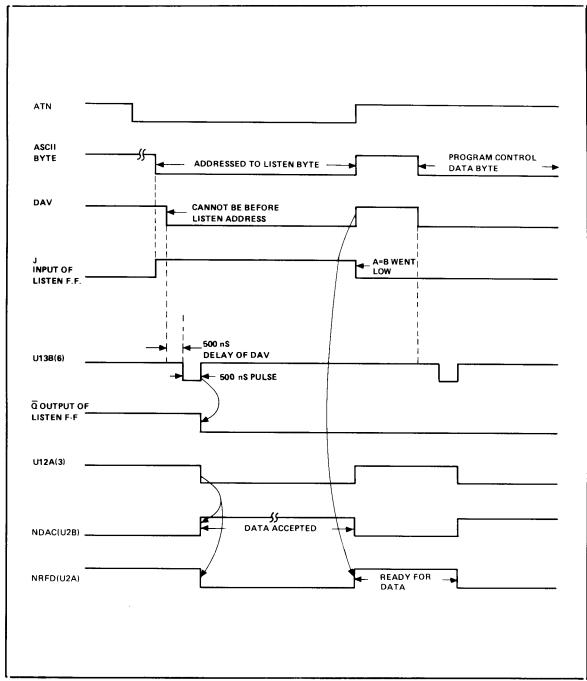

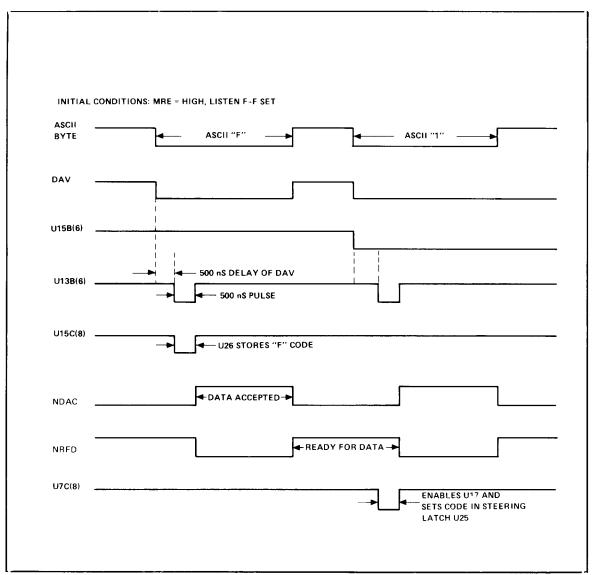

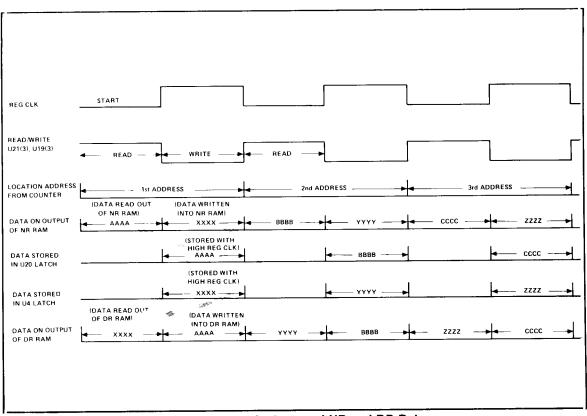

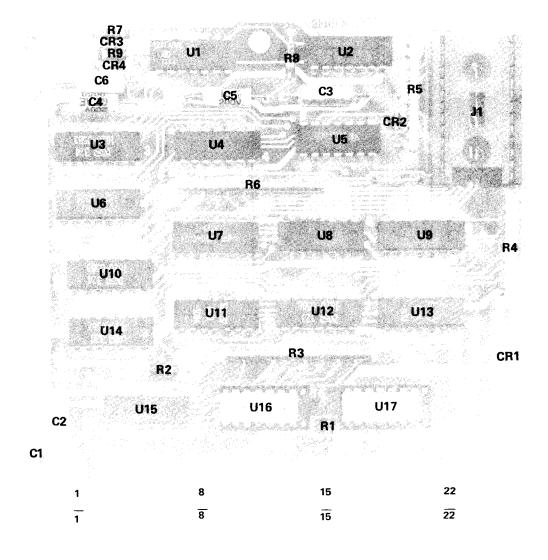

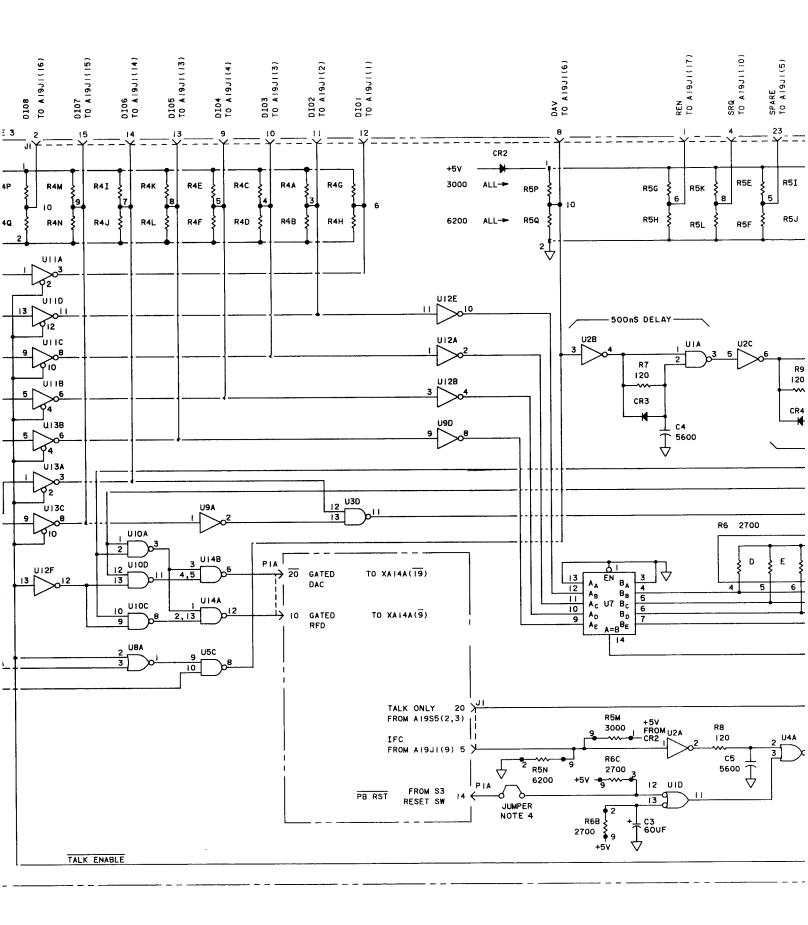

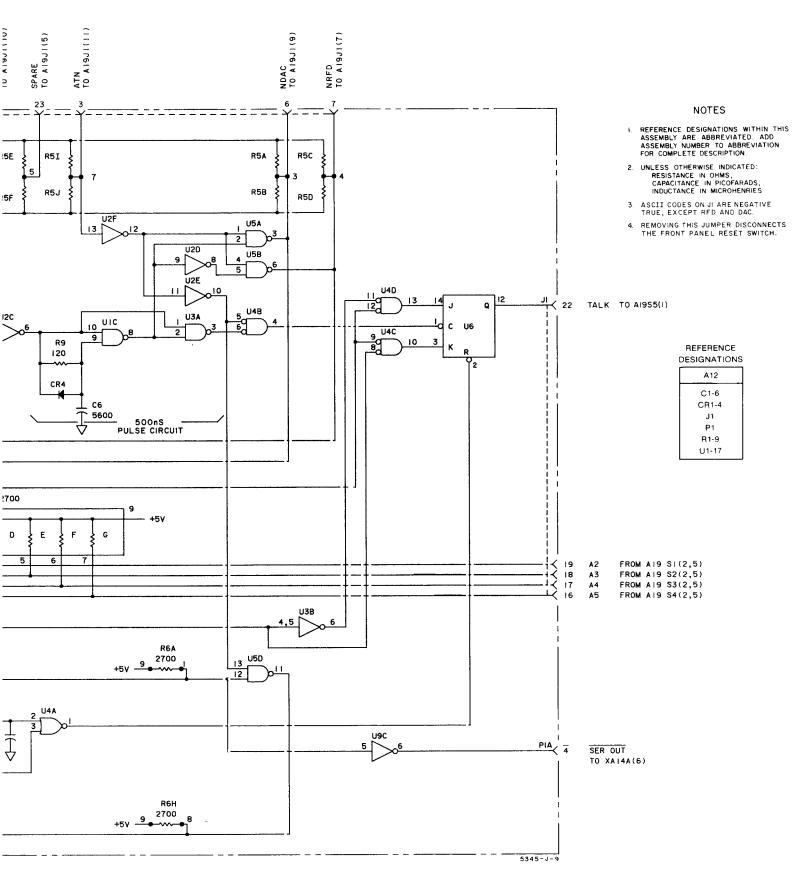

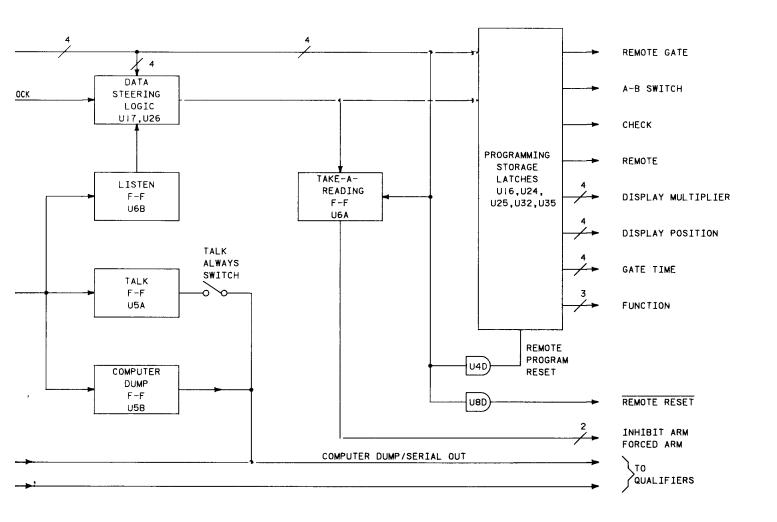

| <b>6-1.</b>  | Replaceable Parts for Standard Instruments Without Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |