N5182B-13

# Information Only Service Note

Supersedes: None

## N5182B X-Series MXG Vector Signal Generator

Serial Numbers: ALL

The Problem – A3 RF assembly boards showing Heater and Unlock errors

Parts Required:

Description P/N Qty.

NONF

Х

ADMINISTRATIVE INFORMATION

[[]] Calibration Required Calibration NOT Required **PRODUCT LINE: 15** AUTHOR: PY

ADDITIONAL INFORMATION:

#### Situation:

Recently we noticed several A3 RF Assemblies return to factory with the following Heater and Unlock errors at the Annunciators area. It can also include errors 619, FPGA revision is invalid. Do refer to Figure 1a and 1b for the details.

Figure 1a – Heater and Unlock Errors with Invalid FPGA Rev #

| REQUENCY 6.0             | 00 000 00                    | 0 000 вн                             | Z         | OFF<br>-144 | .00  | dBm  |

|--------------------------|------------------------------|--------------------------------------|-----------|-------------|------|------|

|                          | HEATER                       |                                      |           |             | UN   | LOCK |

| nstalled Boa<br>lame     | rd Information<br>Part#/Rev# | Serial#                              | HUID      | OFR PIC     | Opts | Extr |

| Analog F                 | N5180-69238<br>PGA 0,0000,00 |                                      | 0000      | 000 000     | 0000 | 0000 |

| Ref FPGA<br>Synth FP     |                              |                                      | nvalid Fl | PGA Rev#    |      |      |

| B<br>IF FPGA<br>BBG FPGA | 2,0c11,01                    | 23140900119<br>38:f2a7<br>,1000:e88e | 0000      | 000 000     | 0000 | 0000 |

Or

| FREQ        | UENCY                         |                                                      |                                          | RF OF      |       |         |        |      |

|-------------|-------------------------------|------------------------------------------------------|------------------------------------------|------------|-------|---------|--------|------|

|             | 6.000                         | 000 000                                              | 0 0 0 GHz                                | z -1       | .44   | 00.1    | dBr    | 1    |

|             |                               | HEATER                                               |                                          |            |       |         |        | ERR  |

|             |                               |                                                      |                                          |            |       |         |        |      |

| Inst<br>Nam | alled Board I<br>e            | information<br>Part#/Rev#                            | Serial#                                  | HUID OFR   | PIC   | Opts    | Extr   |      |

| RF          |                               |                                                      | 23141900058                              | 0000 0000  | 000   | 0000    | 0000   |      |

|             | Analog FPGA                   | ffff,ffff,                                           |                                          |            |       |         |        | - 8  |

|             | PCI FPGA                      | 7,0130,000                                           | 0.1000                                   | Invalid FP | GA Re | v#      |        | - 10 |

|             | Ref FPGA                      | ffff,ffff,                                           | and the same start of the same start and |            |       |         |        | - 8  |

|             | Synth FPGA                    | 0,0000,000                                           | 0:0000                                   |            |       |         |        | _    |

| BB          | IF FPGA<br>BBG FPGA<br>Memory | N5180-60145<br>2,1462,112<br>40d6,1794,<br>2GB + 2GB |                                          | 0000 000   | 000   | 0000    | 0000   |      |

|             |                               |                                                      |                                          |            | 11    | /30/202 | 22 11: | 30   |

Figure 1b – Multiple Error 619

| FREQ          | UENCY<br>6    |          | _  | 0 000    | 00 (  | O GHZ   | _    | <del>if off</del><br>-1 | 42  | 1.00      | dBm           |

|---------------|---------------|----------|----|----------|-------|---------|------|-------------------------|-----|-----------|---------------|

|               |               |          | H  | EATER    |       |         |      |                         |     |           | EF            |

| Error         | ° Quei        | Je       |    |          |       |         |      |                         |     |           |               |

| 619,<br>7).   | FPGA          | revision | is | invalid; | FPGA: | ANALOG  | (fo  | und O,                  | exp | pected    | (neu)<br>1/10 |

| 619,<br>1dbÓ1 | FPGA<br>1501) | revision | is | invalid; | FPGA: | ANALOG  | (fou | und O,                  | exp | pected    | (neu)<br>2/10 |

| 619,<br>2).   | FPGA          | revision | is | invalid; | FPGA: | REFEREN | ICE  | (found                  | 0,  | expected  | (neu)<br>3/10 |

|               | FPGA<br>131a) |          | is | invalid; | FPGA: | REFEREN | ICE  | (found                  | Ο,  | expected  | (neu)<br>4/10 |

|               |               |          |    |          |       |         |      |                         | 1:  | 1/30/2022 | 11:27         |

| FREQUENCY RF OFF<br>6.000 000 000 000 GHz -144.00                                                                                                               | dBm           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| HEATER                                                                                                                                                          | ERR           |

|                                                                                                                                                                 |               |

| Error Queue                                                                                                                                                     |               |

| 619, FPGA revision is invalid; FPGA: SYNTH (found O, expected 12d).                                                                                             | (neu)<br>5/10 |

| 617, Configuration Error; The backup memory contains license keys<br>for serial number CN83000142. Use the service procedure to<br>overwrite the backup memory. | (neu)<br>6/10 |

| 533, RF Analog FPGA DCM unlocked                                                                                                                                | (neu)<br>7/10 |

| 508, Synthesizer Unlocked; FracN Loop.                                                                                                                          | (neu)<br>8/10 |

| 11/30/2022                                                                                                                                                      | 11:28         |

#### Solution/Action:

This Service Note is to emphasize on the proper handling of the A3 RF Assembly board during removal and replacement procedure in use together with the X-Series Signal Generator Service Guide (N5180-90059), Assembly Replacement Section for A3 RF assembly.

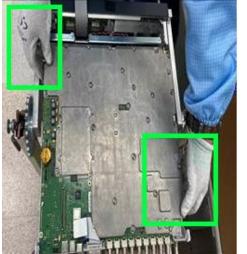

For removal, pry slots are provided on both sides of the A3 RF assembly to aid in removing of the board. Use a flat head (a wedge-shaped flat tip) screwdriver to loosen the board from the chassis as shown in Figure 2.

Figure 2

Always hold the board at the area highlighted in green as shown in Figure 3.

#### Figure 3

Avoid holding the board at the PCB area as shown in Figure 4.

Figure 4

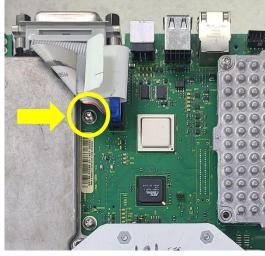

Another precaution is when removing and reinstalling back the screw (refer to Figure 5), it is not necessary to remove the ribbon cable to avoid re-attaching the ribbon cable back.

### Figure 5

#### **Revision History:**

| Date        | Service<br>Note<br>Revision | Author       | Reason for Change |  |

|-------------|-----------------------------|--------------|-------------------|--|

| 13 Dec 2022 | 01                          | Petrina Yong | As Published      |  |

© Keysight Technologies 2015-2022 Information Only Service Note Version 1.2 | December 13, 2022| Page **6** of **6**